# GigaDevice Semiconductor Inc.

GD32F130xx ARM® Cortex®-M3 32-bit MCU

**Datasheet**

# **Table of Contents**

| Ta | able o | of Contents                                          | 1    |

|----|--------|------------------------------------------------------|------|

| Li | st of  | Figures                                              | 3    |

| Li | st of  | Tables                                               | 4    |

| 1. | Ge     | neral descriptionn                                   | 5    |

| 2. |        | vice overview                                        |      |

|    | 2.1.   | Device information                                   |      |

|    |        |                                                      |      |

|    | 2.2.   | Block diagram                                        |      |

|    | 2.3.   | Pinouts and pin assignment                           |      |

|    | 2.4.   | Memory map                                           |      |

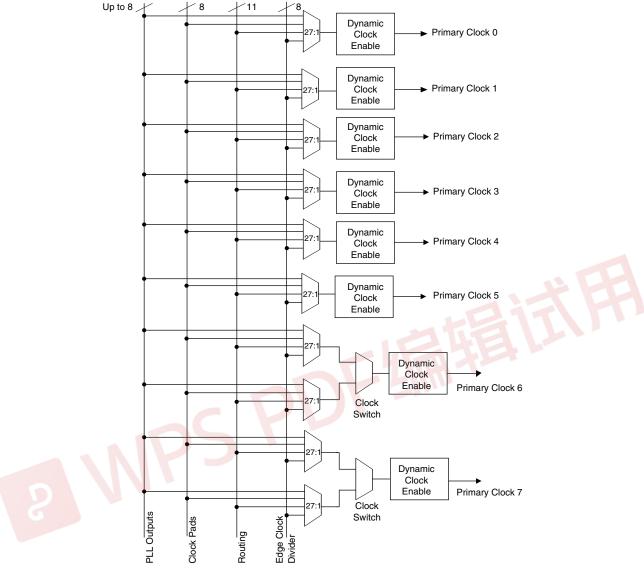

|    | 2.5.   | Clock tree                                           |      |

|    | 2.6.   | Pin definitions                                      |      |

|    | 2.6.   | 1. GD32F130R8 LQFP64 pin definitions                 | . 14 |

|    | 2.6.   | 2. GD32F130Cx LQFP48 pin definitions                 | . 18 |

|    | 2.6.   | 3. GD32F130Kx LQFP32 pin definitions                 | . 21 |

|    | 2.6.   |                                                      |      |

|    | 2.6.   | 5. GD32F130Gx QFN28 pin definitions                  | . 26 |

|    | 2.6.   | 6. GD32F1 <mark>3</mark> 0Fx TSSOP20 pin definitions | . 28 |

|    | 2.6.   | 7. GD32F130xx pin alternate functions                | . 30 |

| 3. | Fu     | nctional description                                 | . 33 |

|    | 3.1.   | ARM® Cortex®-M3 core                                 | . 33 |

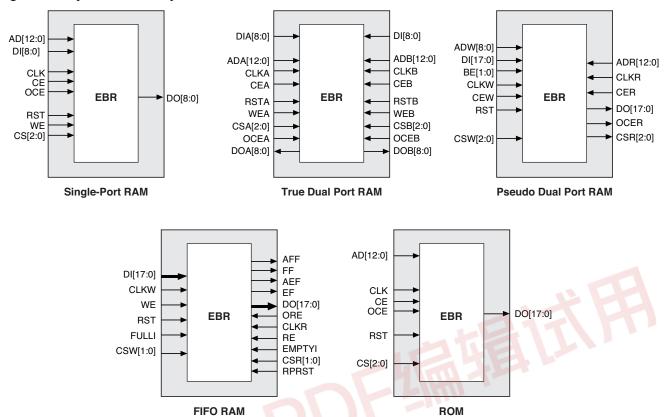

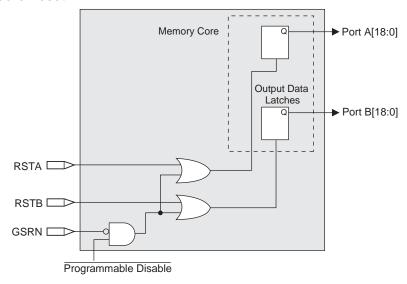

|    | 3.2.   | On-chip memory                                       | . 33 |

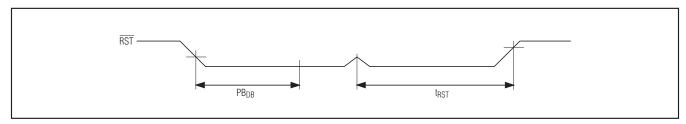

|    | 3.3.   | Clock, reset and supply management                   |      |

|    | 3.4.   | Boot modes                                           |      |

|    |        |                                                      |      |

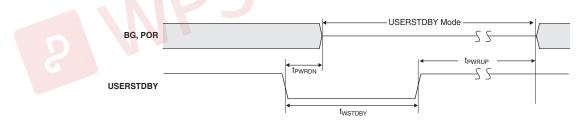

|    | 3.5.   | Power saving modes                                   |      |

|    | 3.6.   | Analog to digital converter (ADC)                    |      |

|    | 3.7.   | DMA                                                  |      |

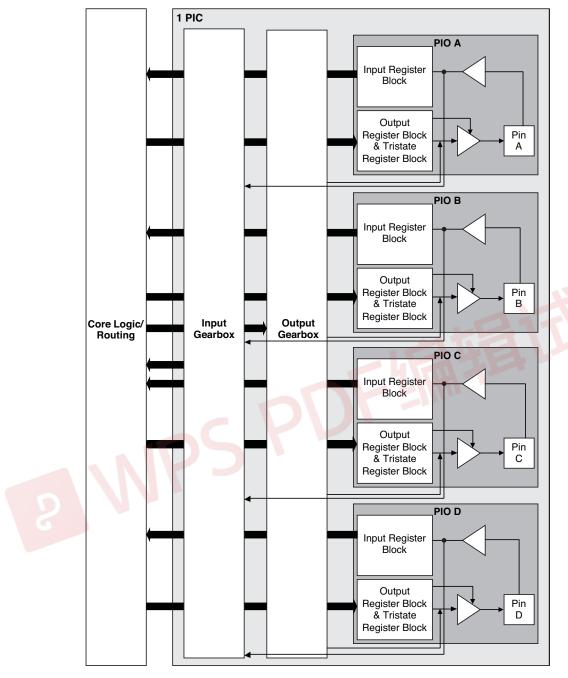

|    | 3.8.   | General-purpose inputs/outputs (GPIOs)               | . 36 |

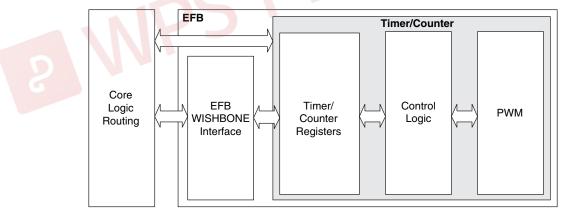

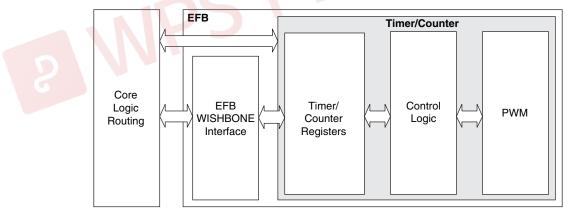

|    | 3.9.   | Timers and PWM generation                            | . 36 |

|    | 3.10.  | Real time clock (RTC)                                | . 37 |

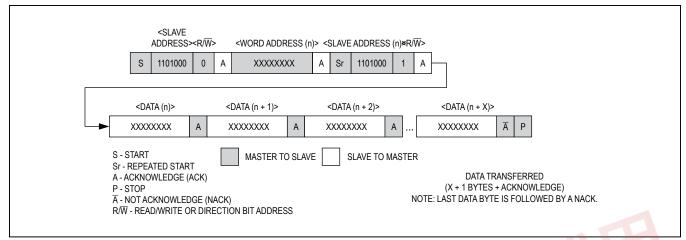

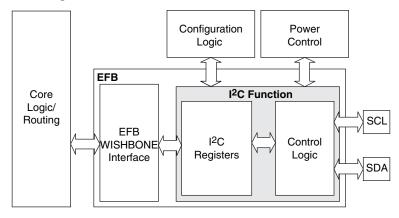

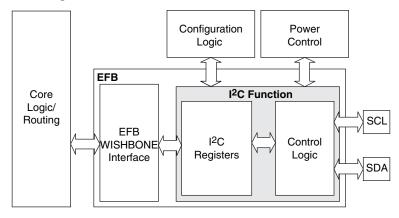

|    | 3.11.  | Inter-integrated circuit (I2C)                       | . 38 |

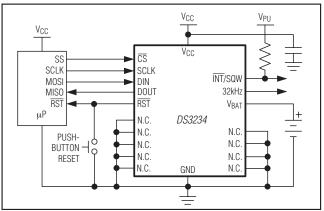

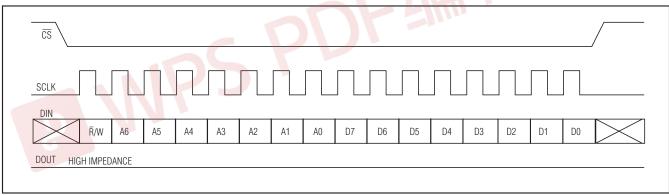

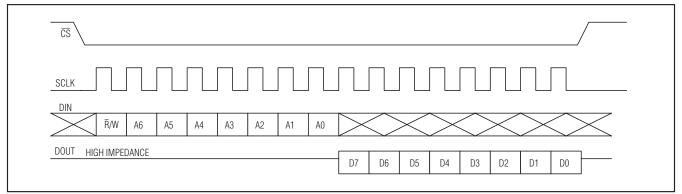

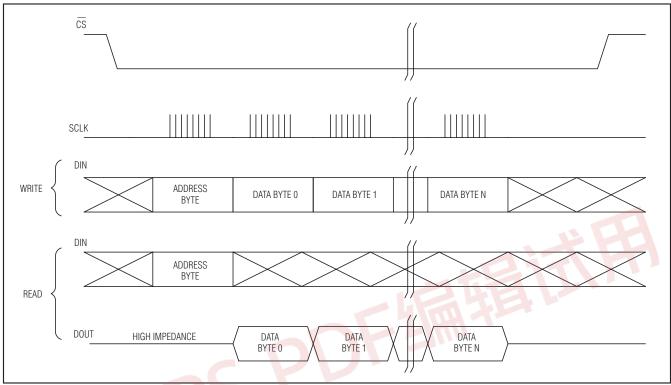

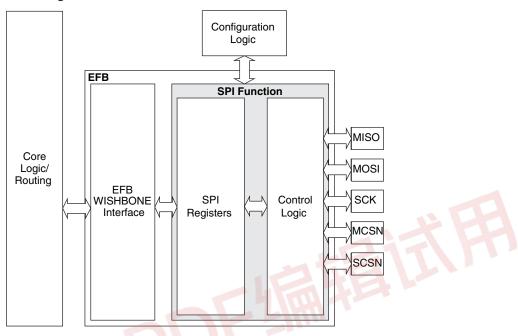

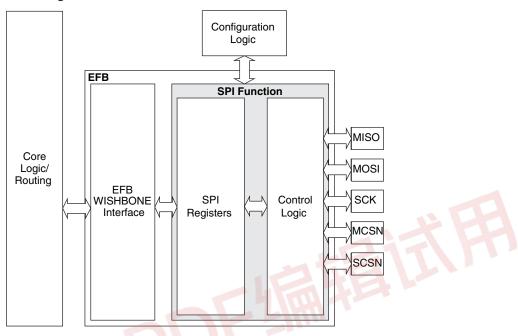

|    | 3.12.  | Serial peripheral interface (SPI)                    | . 38 |

|    | 3.13. | Universal synchronous asynchronous receiver transmitter (USART) | 38 |

|----|-------|-----------------------------------------------------------------|----|

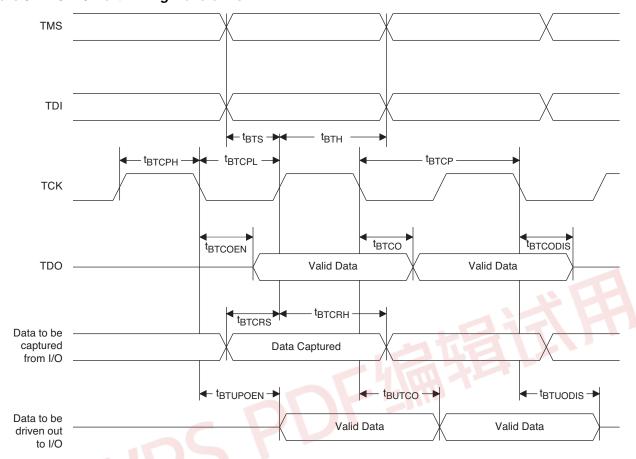

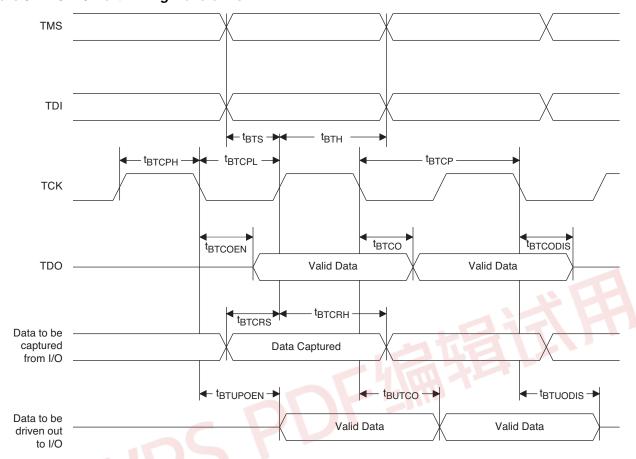

|    | 3.14. | Debug mode                                                      | 39 |

|    | 3.15. | Package and operation temperature                               | 39 |

| 4. | Ele   | ctrical characteristics                                         | 40 |

|    | 4.1.  | Absolute maximum ratings                                        | 40 |

|    | 4.2.  | Recommended DC characteristics                                  | 40 |

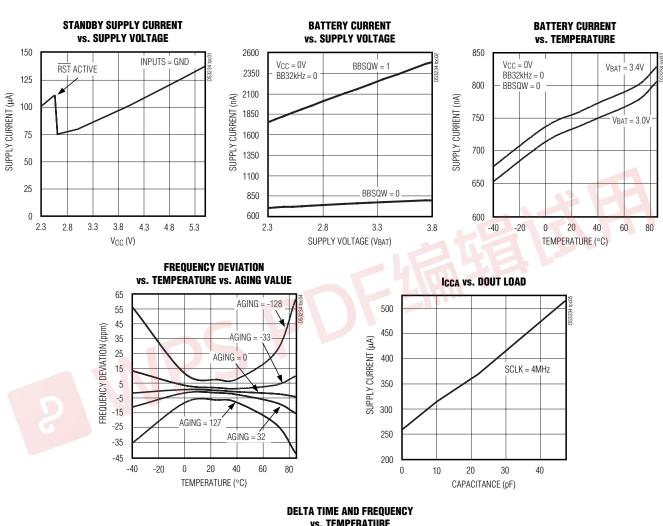

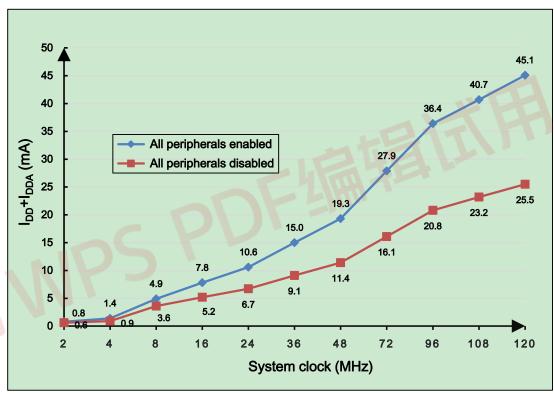

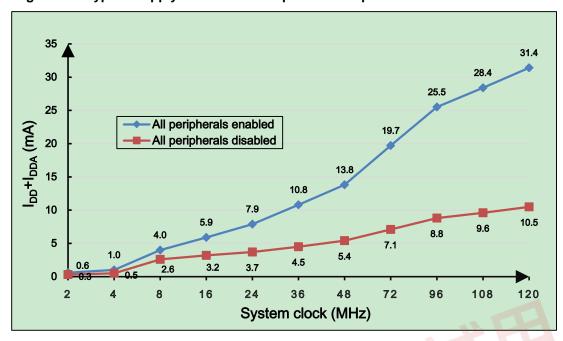

|    | 4.3.  | Power consumption                                               | 41 |

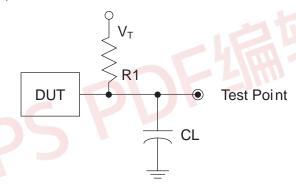

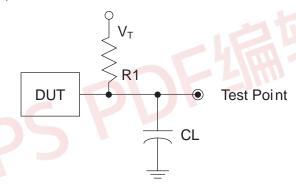

|    | 4.4.  | EMC characteristics                                             | 42 |

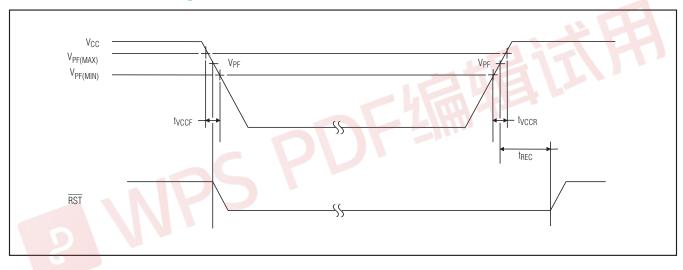

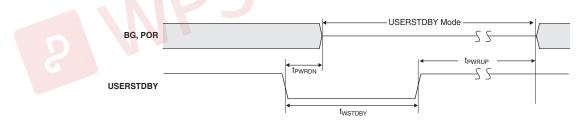

|    | 4.5.  | Power supply supervisor characteristics                         | 42 |

|    | 4.6.  | Electrical sensitivity                                          | 43 |

|    | 4.7.  | External clock characteristics                                  | 43 |

|    | 4.8.  | Internal clock characteristics                                  |    |

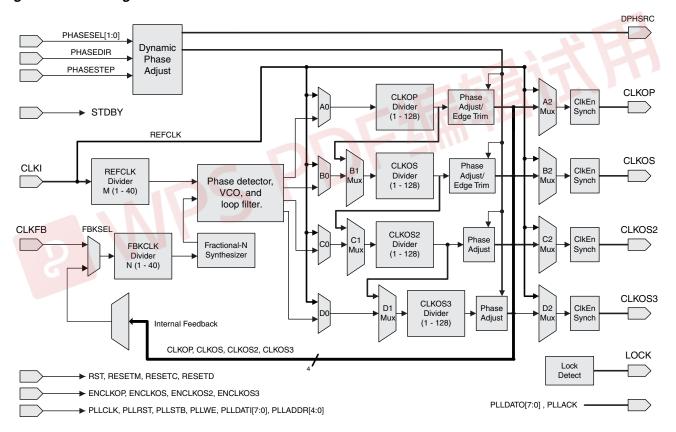

|    | 4.9.  | PLL characteristics                                             |    |

|    | 4.10. | Memory characteristics                                          |    |

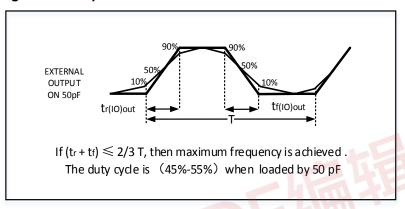

|    | 4.11. | GPIO characteristics                                            |    |

|    | 4.12. | ADC characteristics                                             | 46 |

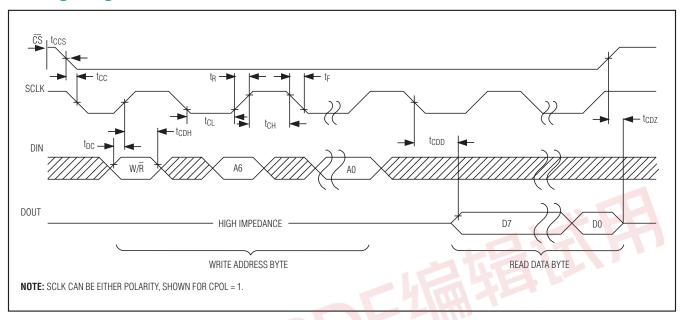

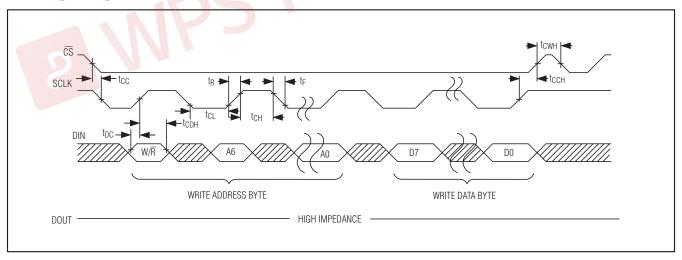

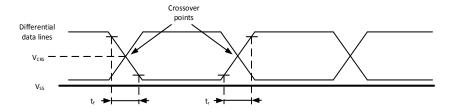

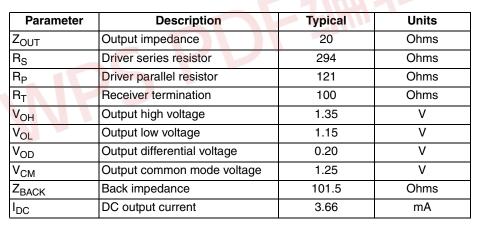

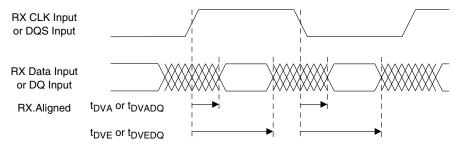

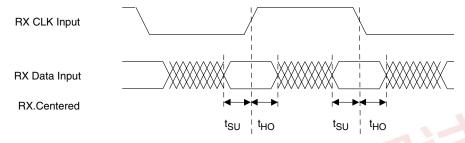

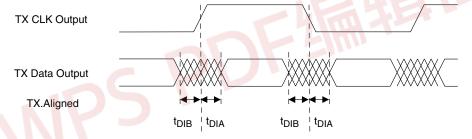

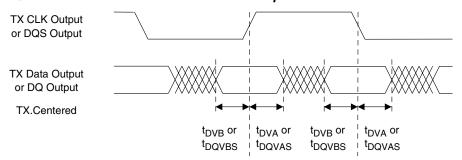

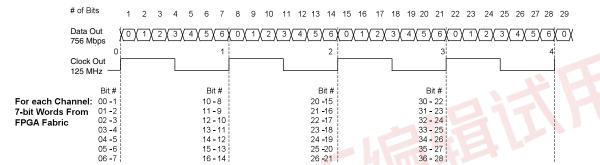

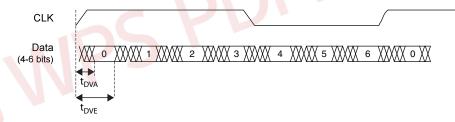

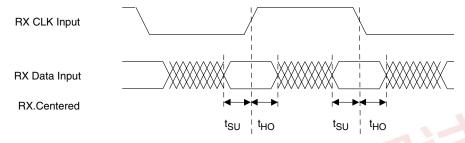

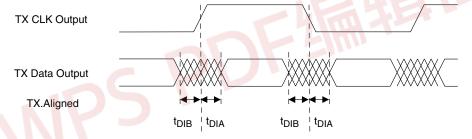

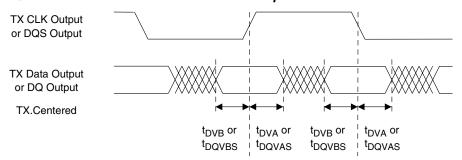

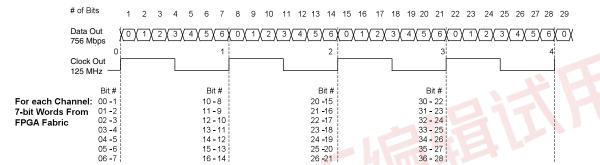

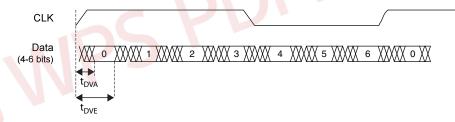

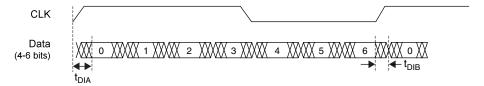

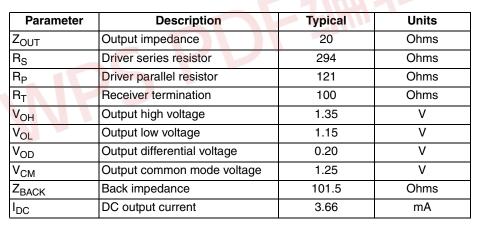

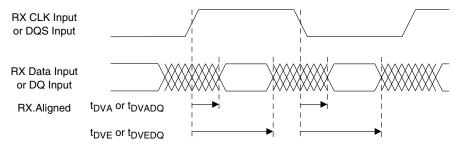

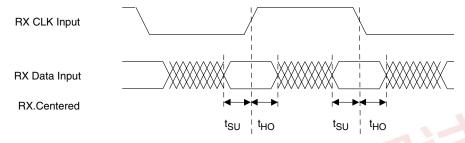

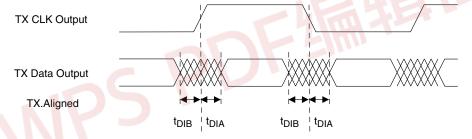

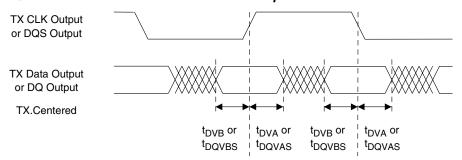

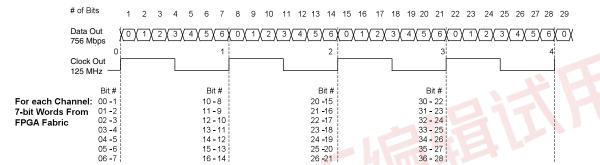

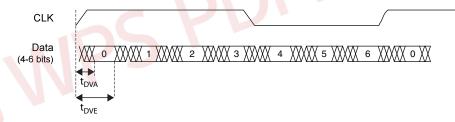

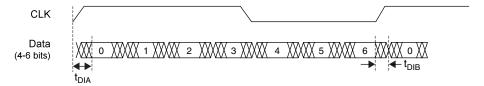

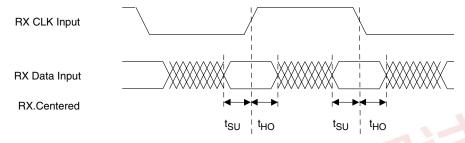

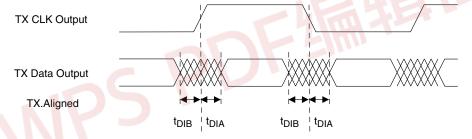

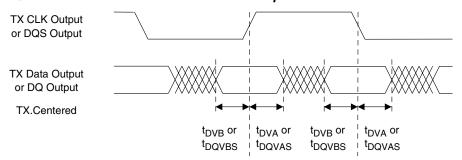

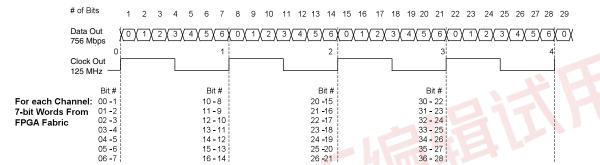

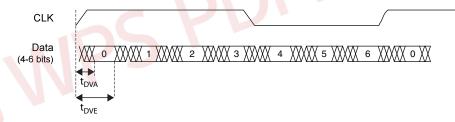

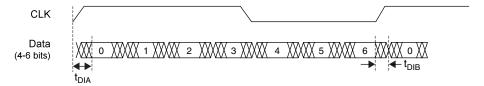

|    | 4.13. | SPI characteristics                                             | 46 |

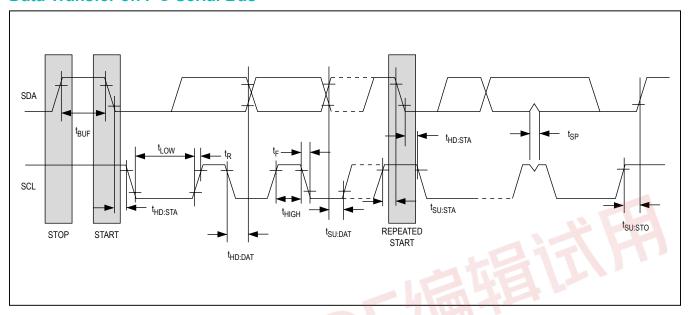

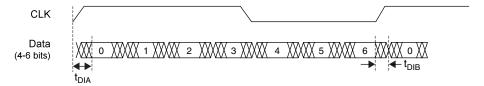

|    | 4.14. | I2C characteristics                                             | 47 |

| 5. | Pac   | kage information                                                | 48 |

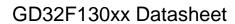

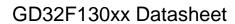

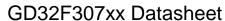

|    | 5.1.  | TSSOP package outline dimensions                                | 48 |

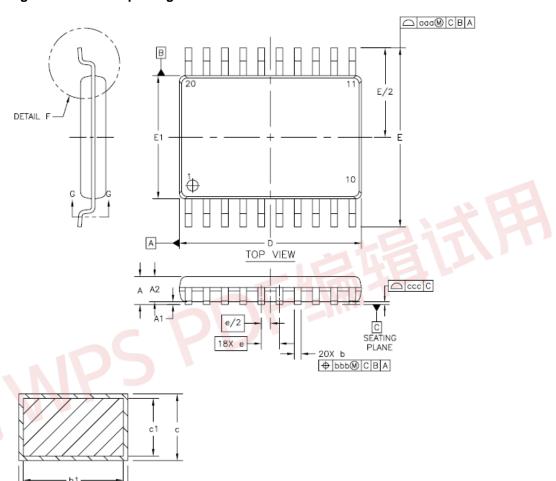

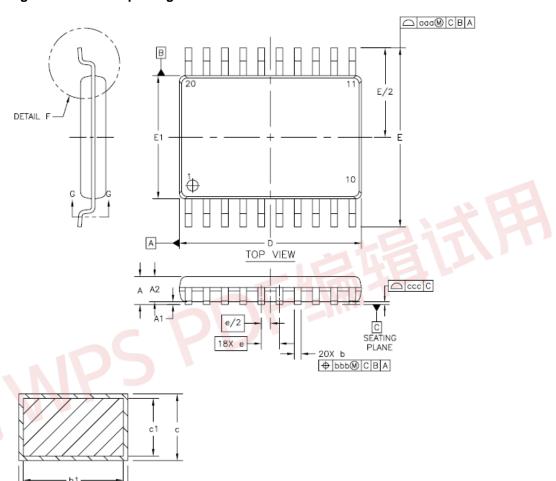

|    | 5.2.  | QFN package outline dimensions                                  | 49 |

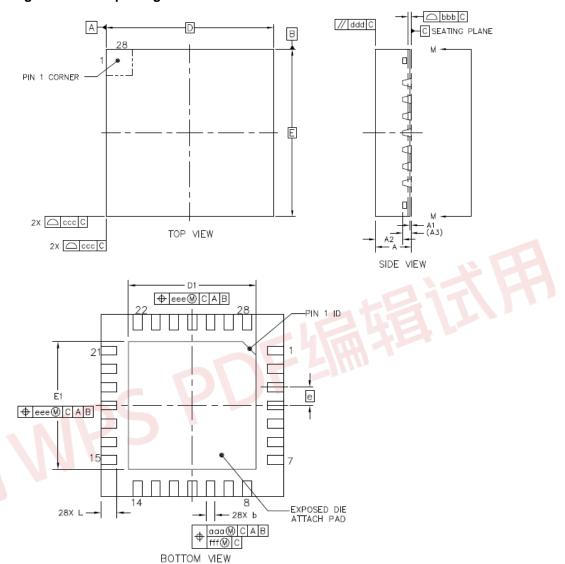

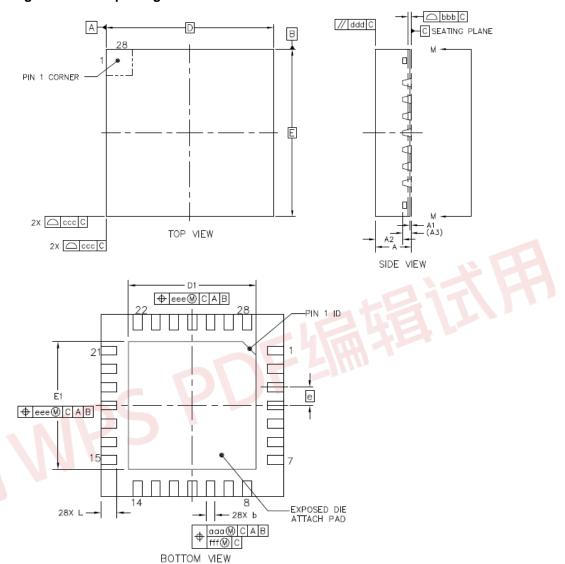

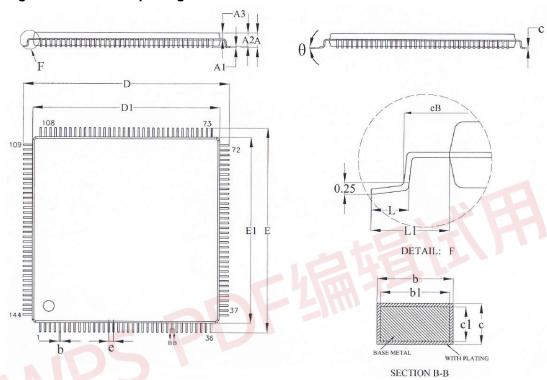

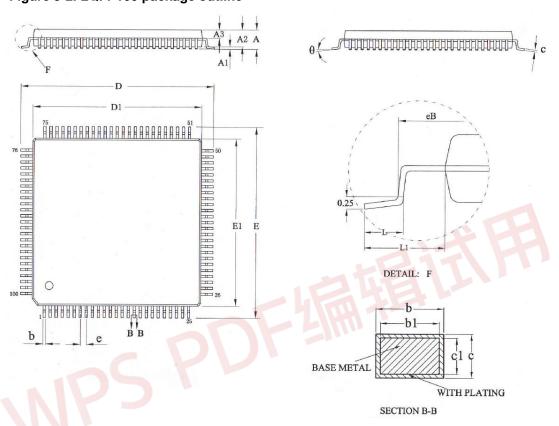

|    | 5.3.  | LQFP package outline dimensions                                 | 51 |

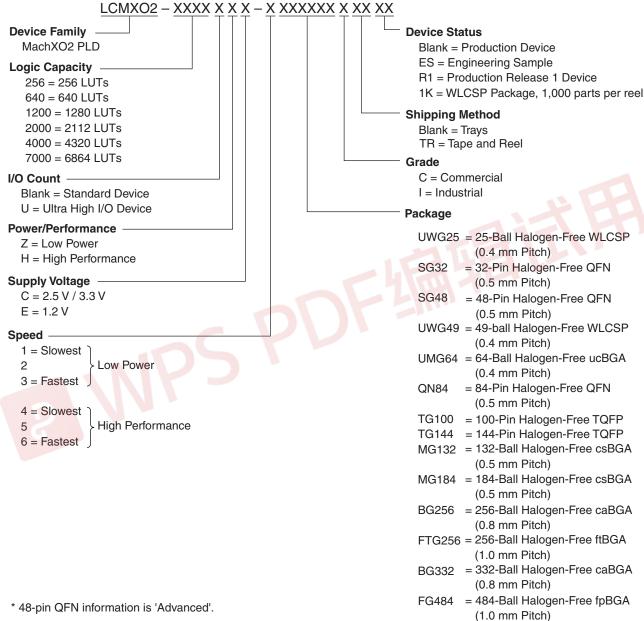

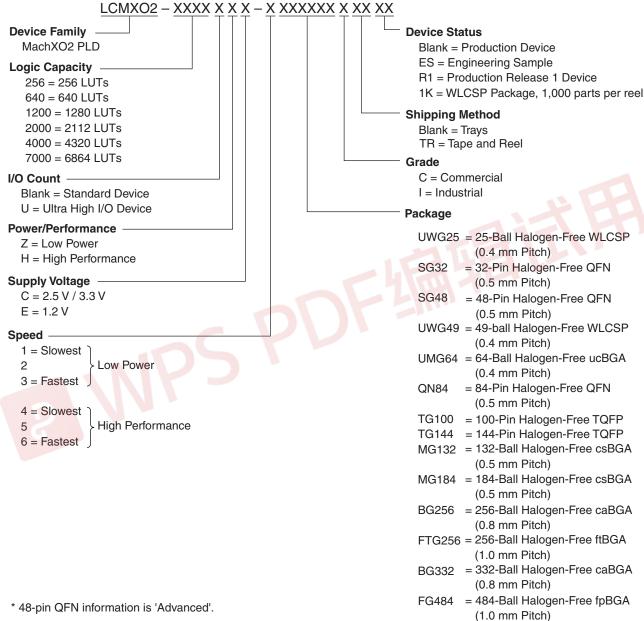

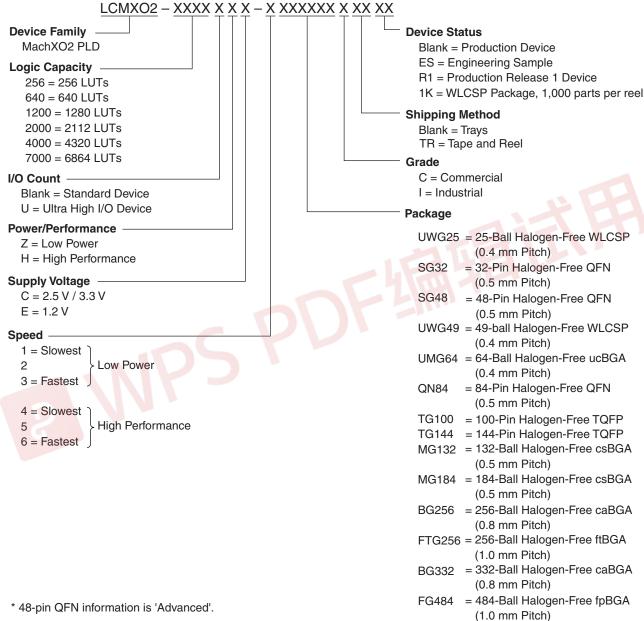

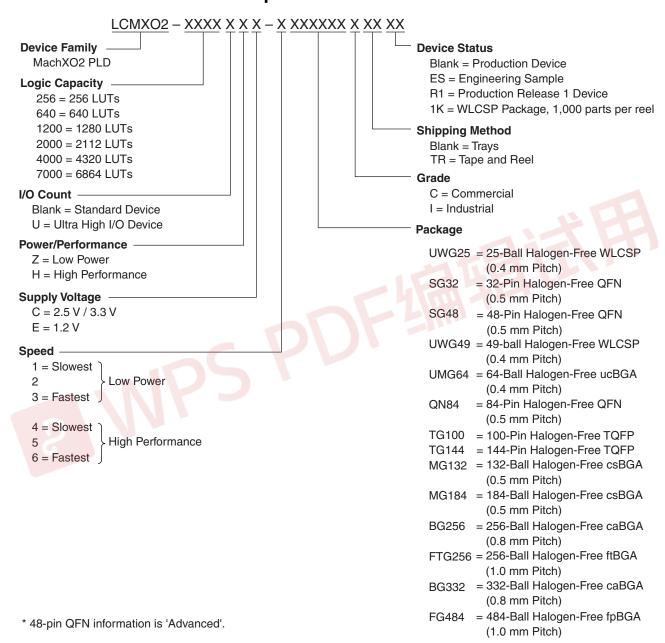

| 6. | Orc   | lering information                                              | 53 |

| 7. | Rev   | vision history                                                  | 54 |

# **List of Figures**

| Figure 2-1. GD32F130xx block diagram   |  |

|----------------------------------------|--|

| Figure 2-2. GD32F130Rx LQFP64 pinouts  |  |

| Figure 2-3. GD32F130Cx LQFP48 pinouts  |  |

| Figure 2-4. GD32F130Cx LQFP32 pinouts  |  |

| Figure 2-5. GD32F130Kx QFN32 pinouts   |  |

| Figure 2-6. GD32F130Gx QFN28 pinouts   |  |

| Figure 2-7. GD32F130Fx TSSOP20 pinouts |  |

| Figure 2-8. GD32F130xx clock tree      |  |

| Figure 5-1. TSSOP package outline      |  |

| Figure 5-2. QFN package outline        |  |

| Figure 5-3, LQFP package outline       |  |

# **List of Tables**

| Table 2-1. GD32F130xx devices features and peripheral list                     | 6                      |

|--------------------------------------------------------------------------------|------------------------|

| Table 2-2. GD32F130xx memory map                                               | 11                     |

| Table 2-3. GD32F130R8 LQFP64 pin definitions                                   | 14                     |

| Table 2-4. GD32F130Cx LQFP48 pin definitions                                   | 18                     |

| Table 2-5. GD32F130Kx LQFP32 pin definitions                                   | 21                     |

| Table 2-6. GD32F130Kx QFN32 pin definitions                                    | 23                     |

| Table 2-7. GD32F130Gx QFN28 pin definitions                                    | 26                     |

| Table 2-8. GD32F130Fx TSSOP20 pin definitions                                  | 28                     |

| Table 2-9. Port A alternate functions summary                                  | 30                     |

| Table 2-10. Port B alternate functions summary                                 | 31                     |

| Table 2-11. Port C & D & F alternate functions summary                         | 32                     |

| Table 4-1. Absolute maximum ratings                                            | 40                     |

| Table 4-2. DC operating conditions                                             | 40                     |

| Table 4-3. Power consumption characteristics                                   | 41                     |

| Table 4-4. EMS characteristics                                                 |                        |

| Table 4-5. EMI characteristics                                                 | 42                     |

| Table 4-6. Power supply supervisor characteristics                             |                        |

| Table 4-7. ESD characteristics                                                 |                        |

| Table 4-8. Static latch-up characteristics                                     | 43                     |

| Table 4-9. High speed crystal oscillator (HXTAL) generated from a crystal/cera | mic characteristics 43 |

| Table 4-10. Low speed crystal oscillator (LXTAL) generated from a crystal/cera | mic characteristics    |

|                                                                                | 44                     |

| Table 4-11. Internal 8 MHz RC oscillator (IRC8M) characteristics               | 44                     |

| Table 4-12. Internal 40KHz RC oscillator (IRC40K) characteristics              | 44                     |

| Ta <mark>ble 4-13. PLL characteristics</mark>                                  |                        |

| Table 4-14. Flash memory characteristics                                       | 45                     |

| Table 4-15. I/O port characteristics                                           | 45                     |

| Table 4-16. ADC characteristics                                                | 46                     |

| Table 4-17. Standard SPI characteristics                                       | 46                     |

| Table 4-18. I2C characteristics                                                | 47                     |

| Table 5-1. TSSOP20 package dimensions                                          | 48                     |

| Table 5-2. QFN package dimensions                                              | 50                     |

| Table 5-3. LQFP package dimensions                                             | 52                     |

| Table 6-1. Part ordering code for GD32F130xx devices                           | 53                     |

| Table 7-1. Revision history                                                    | 54                     |

# 1. General description

The GD32F130xx device belongs to the value line of GD32 MCU family. It is a 32-bit general-purpose microcontroller based on the high performance ARM® Cortex®-M3 RISC core with best ratio in terms of processing power, reduced power consumption and peripheral set. The Cortex®-M3 is a next generation processor core which is tightly coupled with a Nested Vectored Interrupt Controller (NVIC), SysTick timer and advanced debug support.

The GD32F130xx device incorporates the ARM® Cortex®-M3 32-bit processor core operating at 72 MHz frequency with Flash accesses zero wait states to obtain maximum efficiency. It provides up to 64 KB on-chip Flash memory and up to 8 KB SRAM memory. An extensive range of enhanced I/Os and peripherals connected to two APB buses. The devices offer one 12-bit ADC, up to five general 16-bit timers, a general 32-bit timer, a PWM advanced timer, as well as standard and advanced communication interfaces: up to two SPIs, two I2Cs and two USARTs.

The device operates from a 2.6 to 3.6 V power supply and available in -40 to +85 °C temperature range. Several power saving modes provide the flexibility for maximum optimization between wakeup latency and power consumption, an especially important consideration in low power applications.

The above features make the GD32F130xx devices suitable for a wide range of applications, especially in areas such as industrial control, motor drives, user interface, power monitor and alarm systems, consumer and handheld equipment, gaming and GPS, E-bike and so on.

# 2. Device overview

# 2.1. Device information

Table 2-1. GD32F130xx devices features and peripheral list

|              |                              |                 |                   |                |                 |                          |             | )32F13          |                          | -           |                 |                |             |                     |

|--------------|------------------------------|-----------------|-------------------|----------------|-----------------|--------------------------|-------------|-----------------|--------------------------|-------------|-----------------|----------------|-------------|---------------------|

| Part Number  |                              | F4              | F6                | F8             | G4              | G6                       | G8          | K4              | K6                       | K8          | C4              | C6             | C8          | R8                  |

| ı            | Flash (KB)                   |                 | 32                | 64             | 16              | 32                       | 64          | 16              | 32                       | 64          | 16              | 32             | 64          | 64                  |

| ,            | SRAM (KB)                    |                 | 4                 | 8              | 4               | 4                        | 8           | 4               | 4                        | 8           | 4               | 4              | 8           | 8                   |

|              | General<br>timer(32-<br>bit) | 1               | 1 (1)             | 1              | 1               | 1                        | 1           | 1               | 1                        | 1           | 1               | 1 (1)          | 1           | 1 (1)               |

| S            | General<br>timer(16-<br>bit) | 4 (2,13,15-16)  | 4 (2,13,15-16)    | 4 (2,13,15-16) | 4 (2,13,15-16)  | 4 (2,13,15-16)           | 5 (2,13-16) | 4 (2,13,15-16)  | 4 (2,13,15-16)           | 5 (2,13-16) | 4 (2,13,15-16)  | 4 (2,13,15-16) | 5 (2,13-16) | 5 (2,13-16)         |

| Timers       | Advanced timer(16-bit)       | 1               | 1                 | 1              | 1               | 1                        | 1           | 1 (0)           | 1                        | 1           | 1               | 1 (0)          | 1           | 1                   |

|              | SysTick                      | 1               | 1                 | 1              | 1               | 1                        | 1           | 1               | 1                        | 1           | 1               | 1              | 1           | 1                   |

|              | Watchdog                     | 2               | 2                 | 2              | 2               | 2                        | 2           | 2               | 2                        | 2           | 2               | 2              | 2           | 2                   |

|              | RTC                          | 1               | 1                 | 1              | 1               | 1                        | 1           | 1               | 1                        | 1           | 1               | 1              | 1           | 1                   |

|              | USART                        | 1               | 2                 | 2              | 1               | 2                        | 2           | 1               | 2                        | 2           | 1               | 2              | 2           | 2                   |

| Connectivity | I2C                          | (O)<br>1<br>(O) | (0-1)<br><b>1</b> | 2              | (0)<br>1<br>(0) | (0-1)<br><b>1</b><br>(0) | (0-1)       | (0)<br>1<br>(0) | (0-1)<br><b>1</b><br>(0) | (0-1)       | (O)<br>1<br>(O) | 1 (0)          | (0-1)       | (0-1)<br>2<br>(0-1) |

| Sol          | SPI                          | 1               | 1                 | 2              | 1               | 1                        | 2           | 1               | 1                        | 2           | 1               | 1              | 2           | 2                   |

|              | GPIO                         | 15              | 15                | 15             | 23              | 23                       | 23          | 27              | 27                       | 27          | 39              | 39             | 39          | 55                  |

|              | EXTI                         | 16              | 16                | 16             | 16              | 16                       | 16          | 16              | 16                       | 16          | 16              | 16             | 16          | 16                  |

|              | Units                        | 1               | 1                 | 1              | 1               | 1                        | 1           | 1               | 1                        | 1           | 1               | 1              | 1           | 1                   |

| ADC          | Channels<br>(External)       | 9               | 9                 | 9              | 10              | 10                       | 10          | 10              | 10                       | 10          | 10              | 10             | 10          | 16                  |

|              | Channels<br>(Internal)       | 3               | 3                 | 3              | 3               | 3                        | 3           | 3               | 3                        | 3           | 3               | 3              | 3           | 3                   |

|              | Package                      |                 | TSSOP20           |                |                 | QFN28                    |             |                 | QFN32<br>LQFP32          |             |                 | LQFP48         |             |                     |

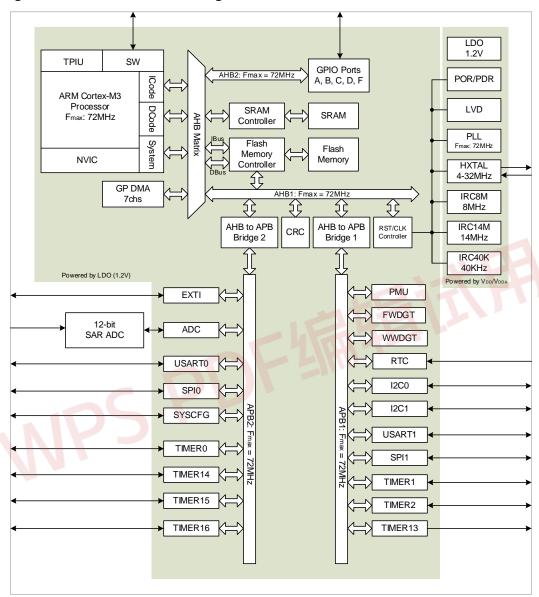

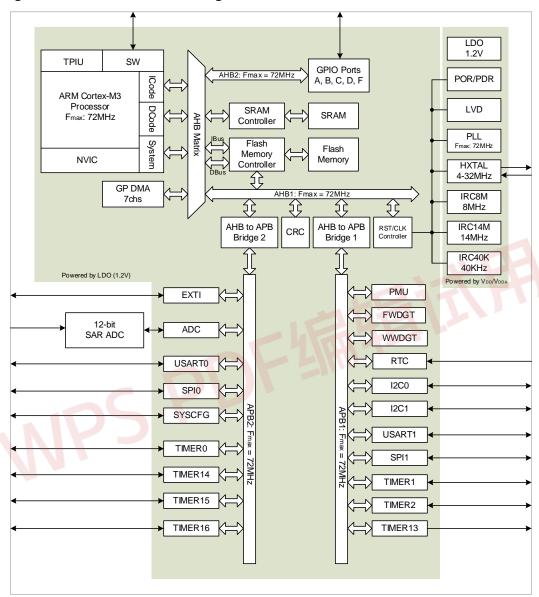

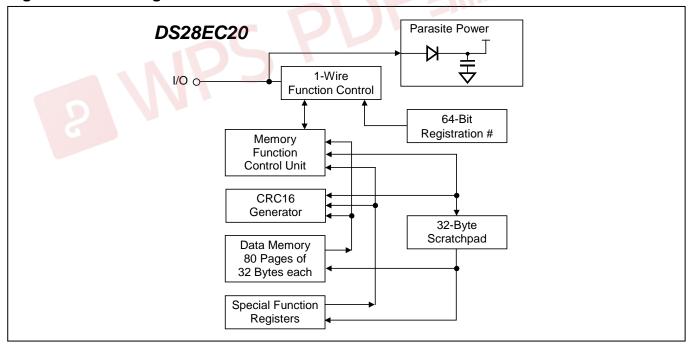

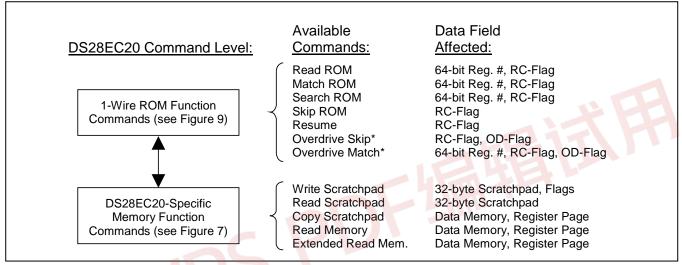

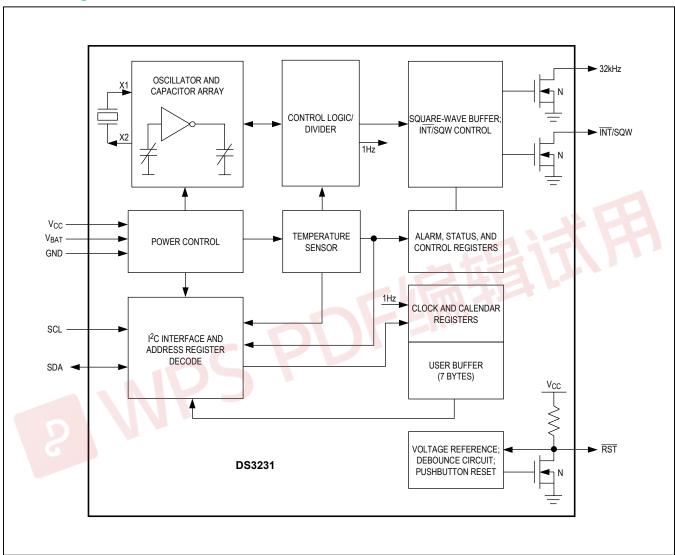

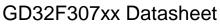

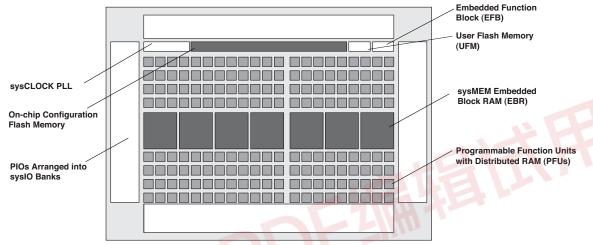

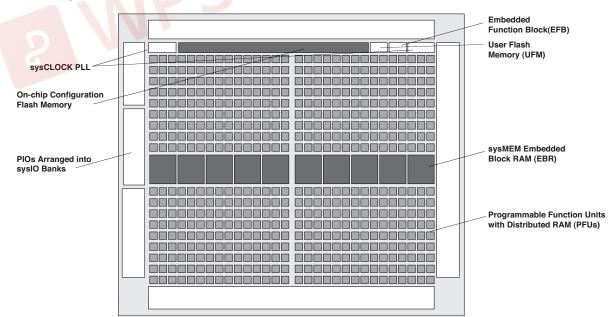

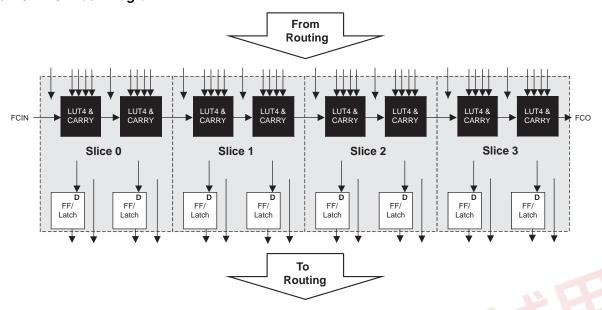

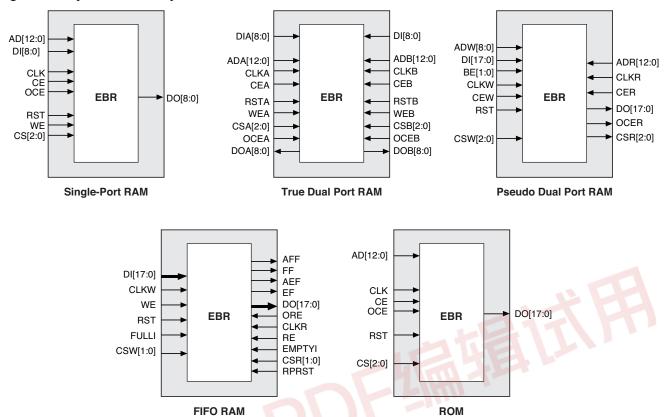

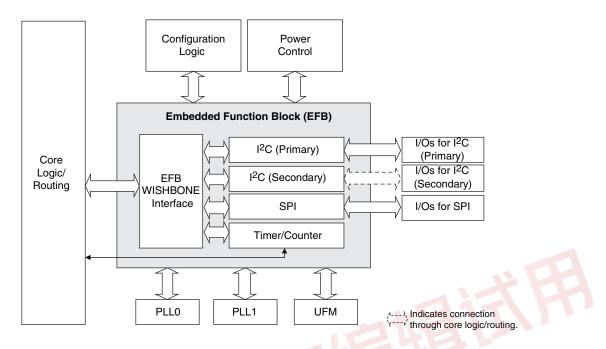

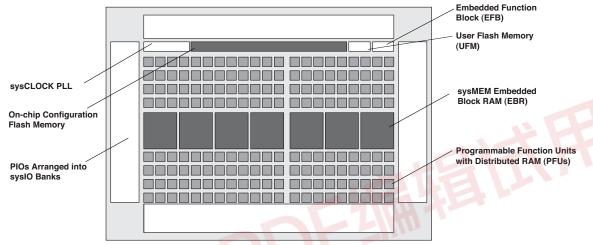

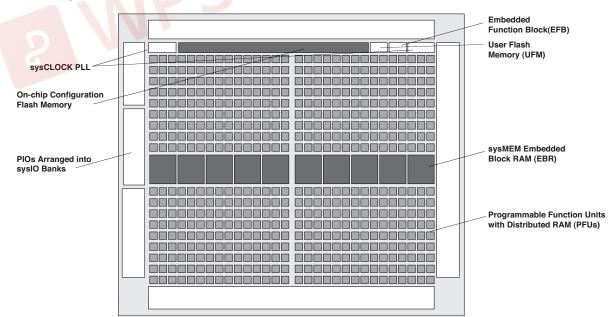

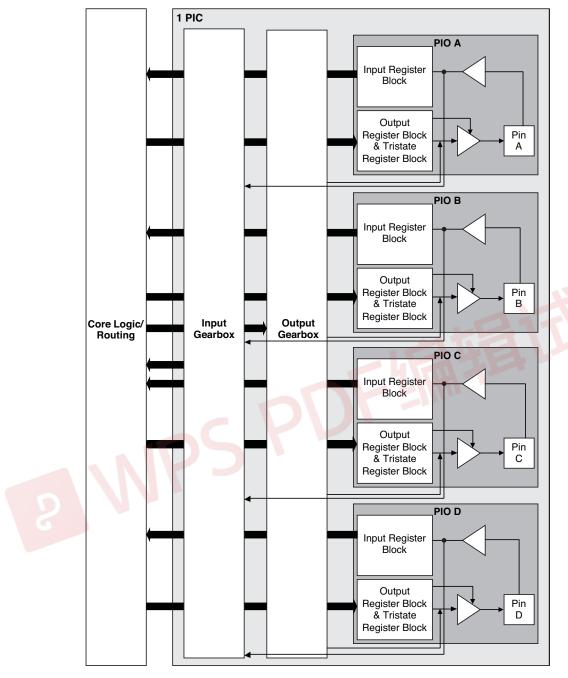

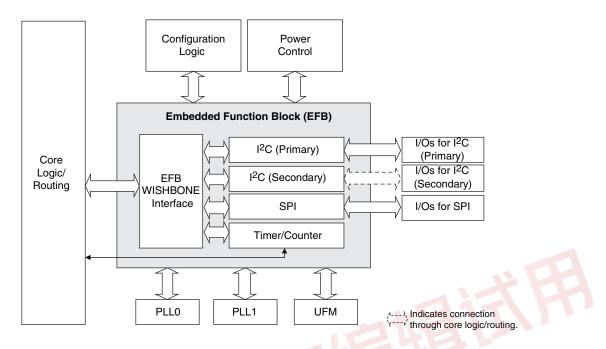

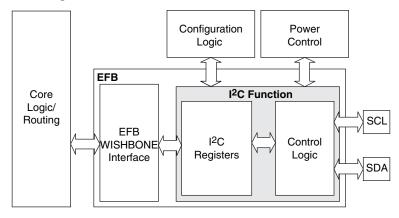

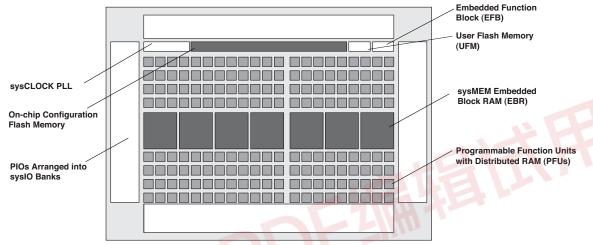

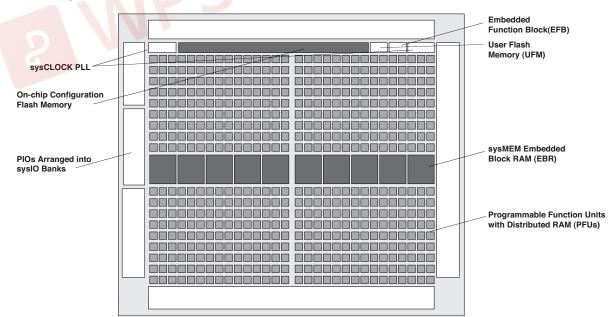

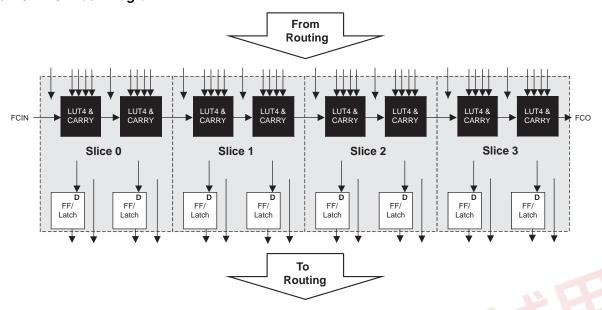

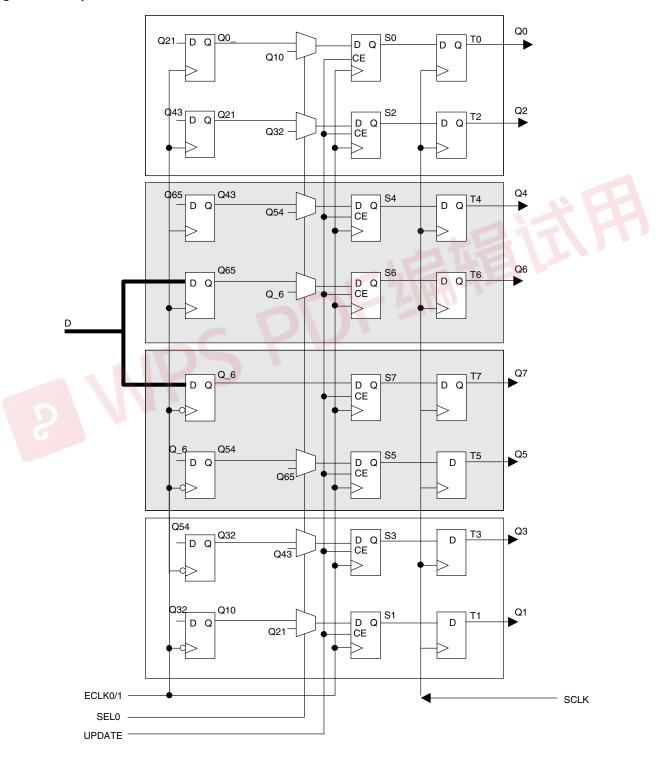

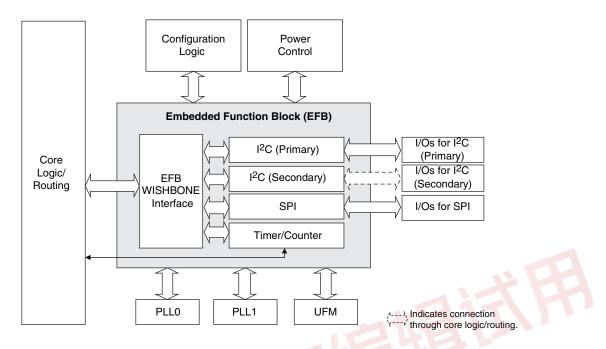

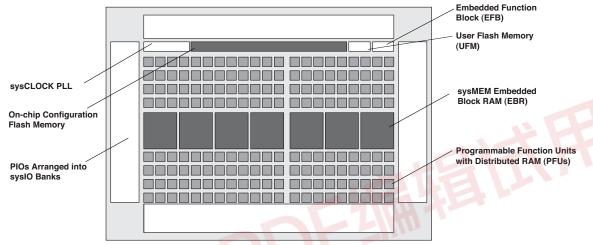

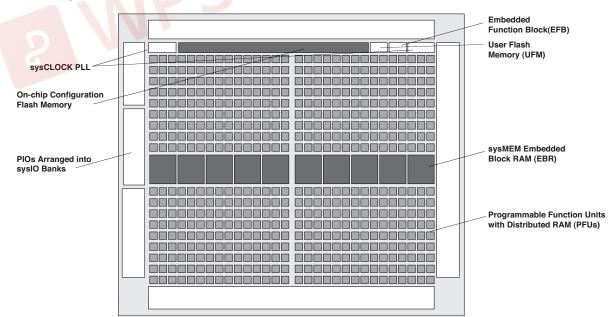

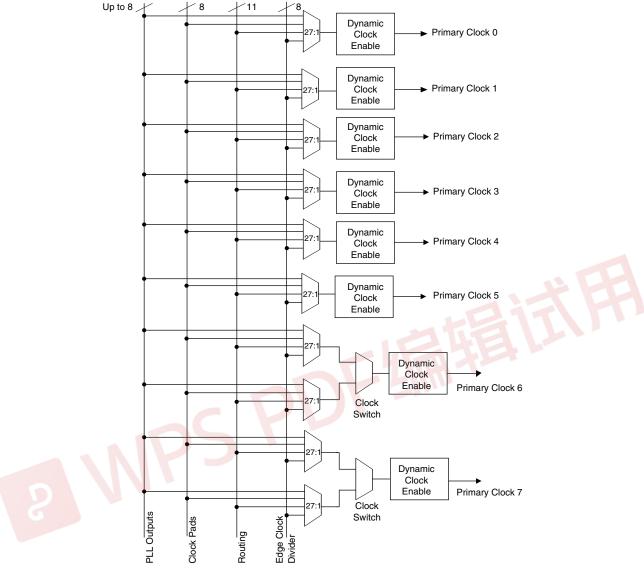

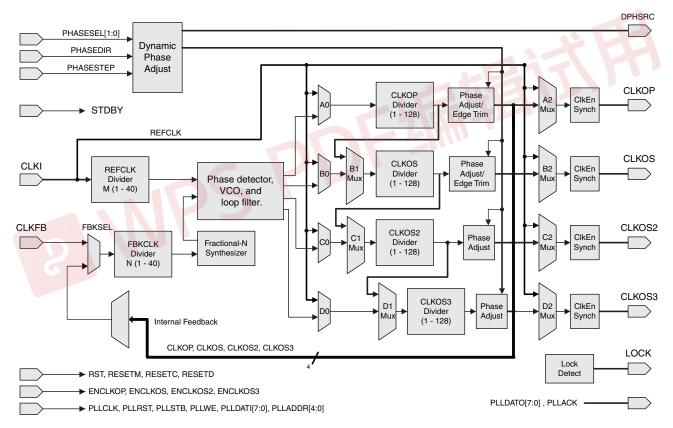

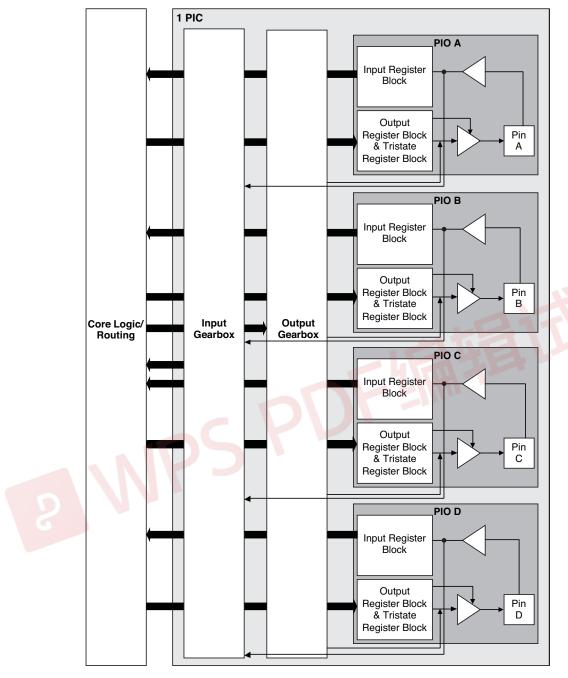

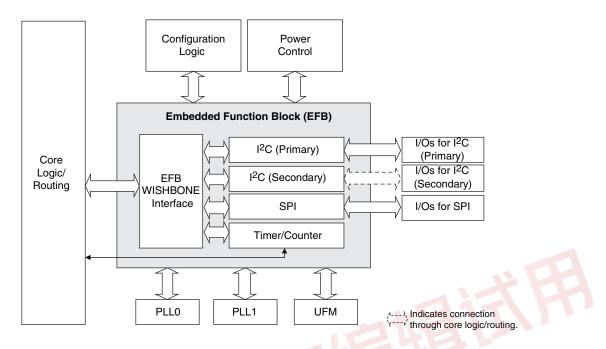

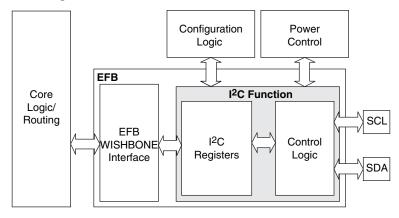

# 2.2. Block diagram

Figure 2-1. GD32F130xx block diagram

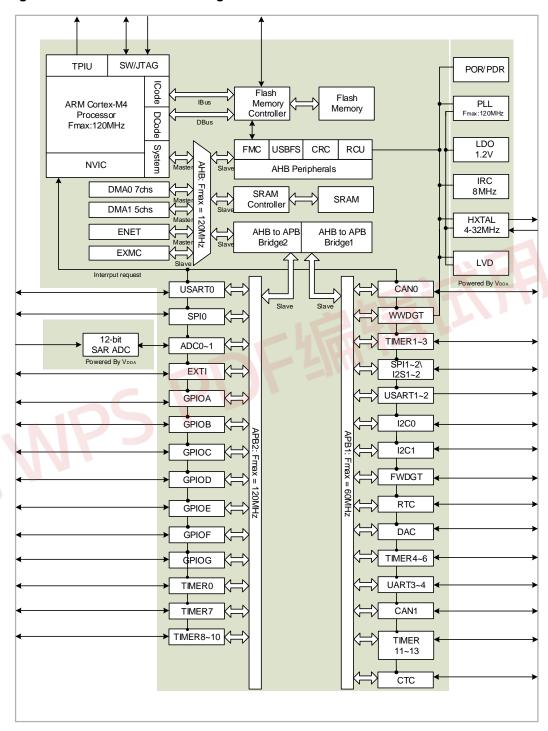

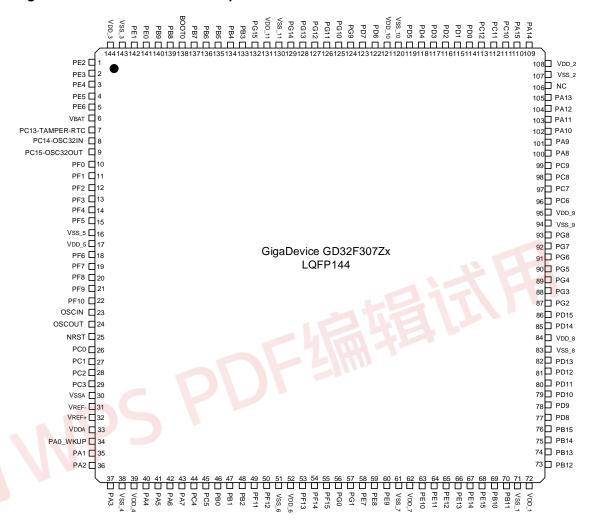

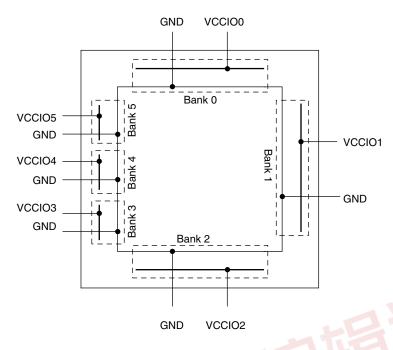

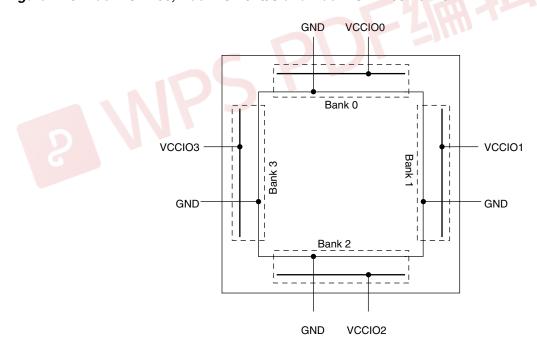

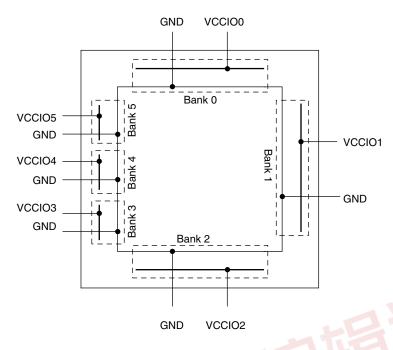

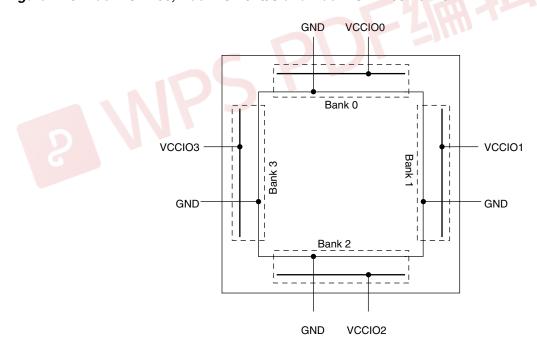

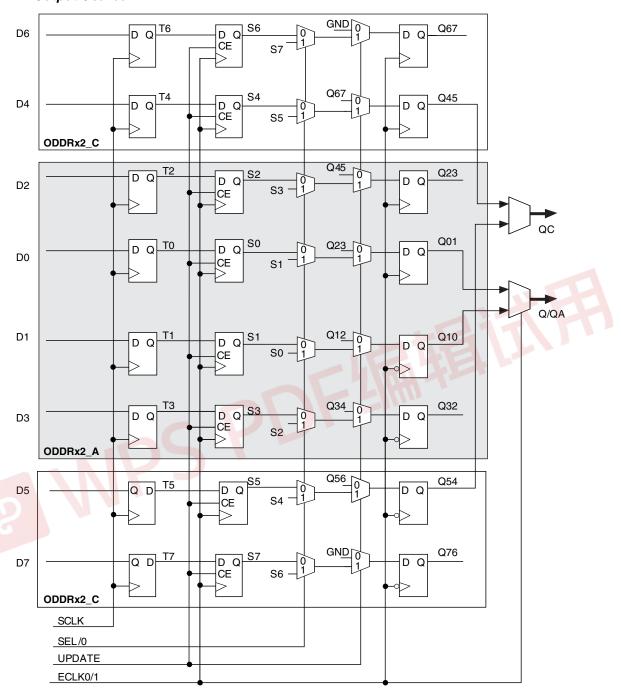

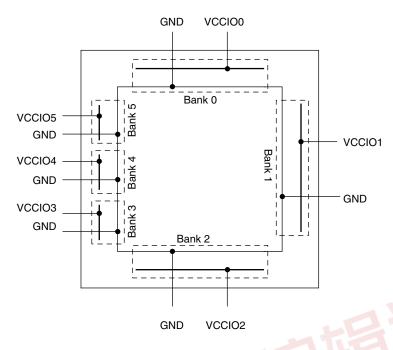

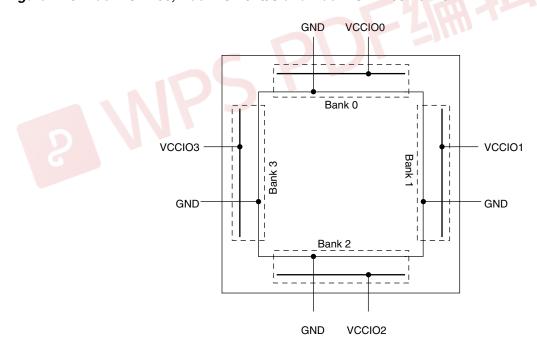

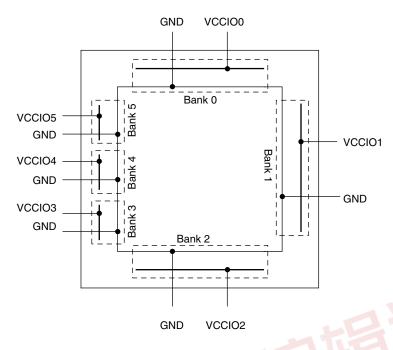

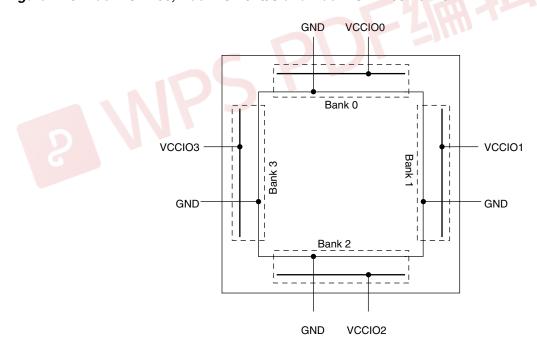

## 2.3. Pinouts and pin assignment

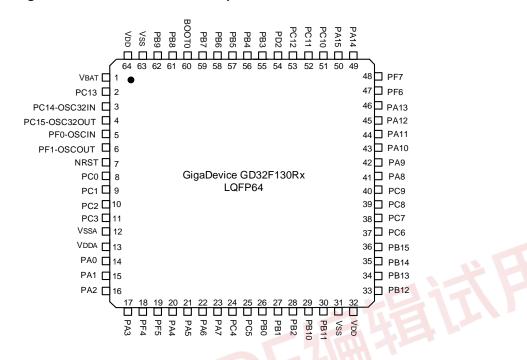

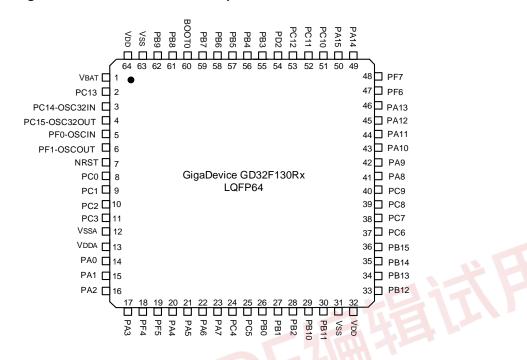

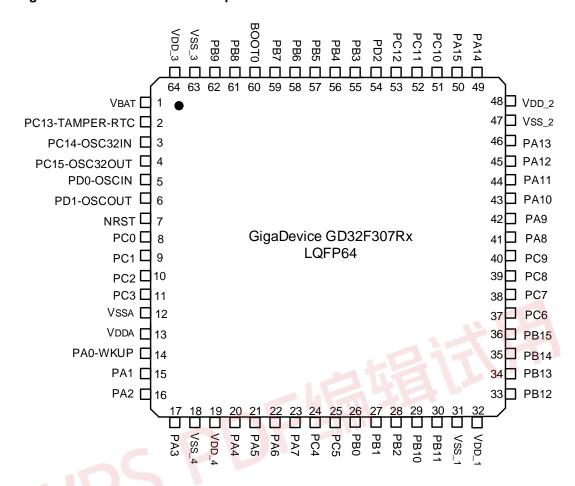

Figure 2-2. GD32F130Rx LQFP64 pinouts

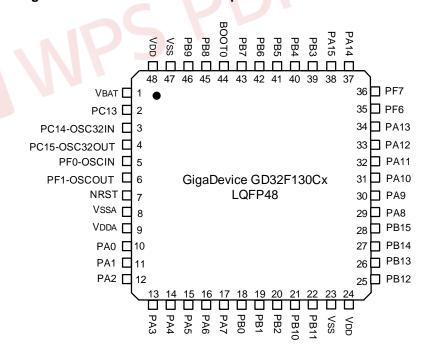

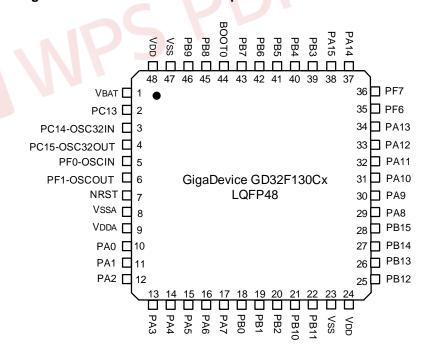

Figure 2-3. GD32F130Cx LQFP48 pinouts

Figure 2-4. GD32F130Cx LQFP32 pinouts

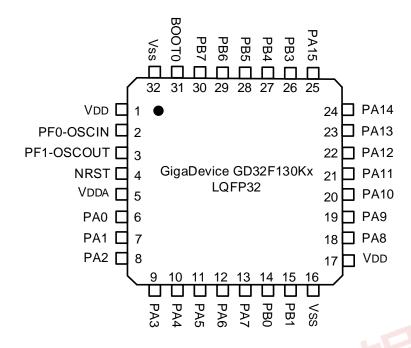

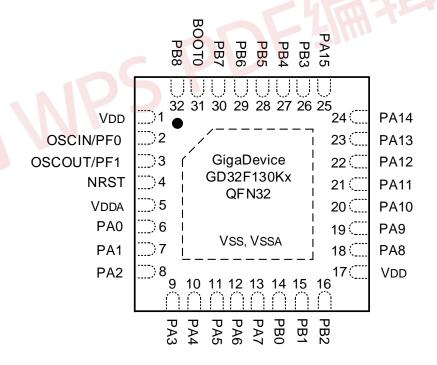

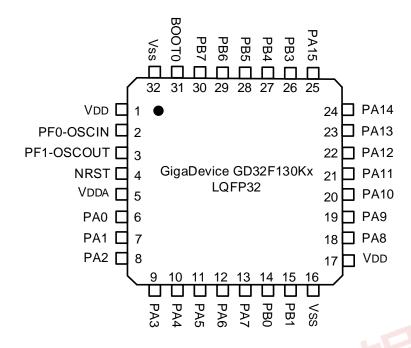

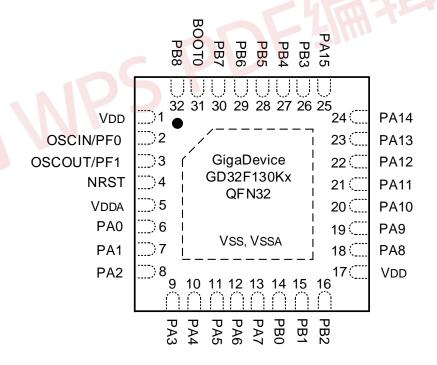

Figure 2-5. GD32F130Kx QFN32 pinouts

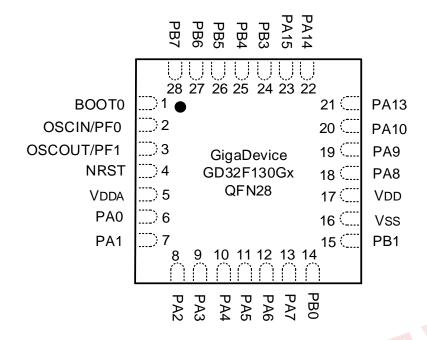

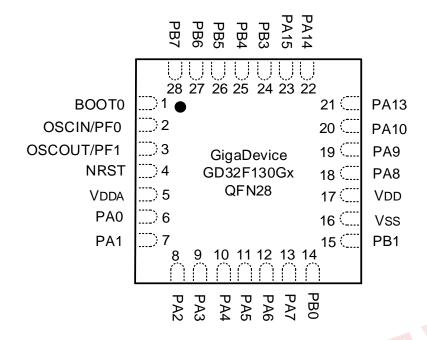

Figure 2-6. GD32F130Gx QFN28 pinouts

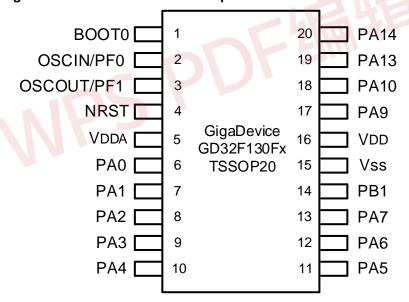

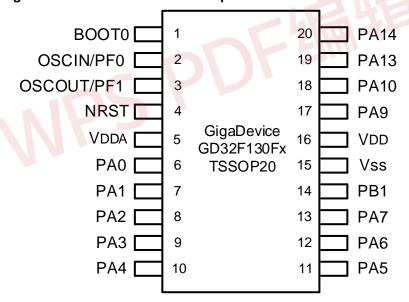

Figure 2-7. GD32F130Fx TSSOP20 pinouts

# 2.4. Memory map

Table 2-2. GD32F130xx memory map

| Pre-defined     |      |                           |                                |

|-----------------|------|---------------------------|--------------------------------|

| Regions         | Bus  | Address                   | Peripherals                    |

|                 |      | 0xE000 0000 - 0xE00F FFFF | Cortex-M3 internal peripherals |

| External Device |      | 0xA000 0000 - 0xDFFF FFFF | Reserved                       |

| External RAM    |      | 0x6000 0000 - 0x9FFF FFFF | Reserved                       |

|                 | AHB1 | 0x5000 0000 - 0x5FFF FFFF | Reserved                       |

|                 |      | 0x4800 1800 - 0x4FFF FFFF | Reserved                       |

|                 |      | 0x4800 1400 - 0x4800 17FF | GPIOF                          |

|                 |      | 0x4800 1000 - 0x4800 13FF | Reserved                       |

|                 | AHB2 | 0x4800 0C00 - 0x4800 0FFF | GPIOD                          |

|                 |      | 0x4800 0800 - 0x4800 0BFF | GPIOC                          |

|                 |      | 0x4800 0400 - 0x4800 07FF | GPIOB                          |

|                 |      | 0x4800 0000 - 0x4800 03FF | GPIOA                          |

|                 |      | 0x4002 4400 - 0x47FF FFFF | Reserved                       |

|                 |      | 0x4002 4000 - 0x4002 43FF | Reserved                       |

|                 |      | 0x4002 3400 - 0x4002 3FFF | Reserved                       |

|                 |      | 0x4002 3000 - 0x4002 33FF | CRC                            |

|                 | AHB1 | 0x4002 2400 - 0x4002 2FFF | Reserved                       |

|                 |      | 0x4002 2000 - 0x4002 23FF | FMC                            |

|                 |      | 0x4002 1400 - 0x4002 1FFF | Reserved                       |

| INIT            |      | 0x4002 1000 - 0x4002 13FF | RCU                            |

| Dorinharala     |      | 0x4002 0400 - 0x4002 0FFF | Reserved                       |

| Peripherals     |      | 0x4002 0000 - 0x4002 03FF | DMA                            |

|                 |      | 0x4001 4C00 - 0x4001 FFFF | Reserved                       |

|                 |      | 0x4001 4800 - 0x4001 4BFF | TIMER16                        |

|                 |      | 0x4001 4400 - 0x4001 47FF | TIMER15                        |

|                 |      | 0x4001 4000 - 0x4001 43FF | TIMER14                        |

|                 |      | 0x4001 3C00 - 0x4001 3FFF | Reserved                       |

|                 |      | 0x4001 3800 - 0x4001 3BFF | USART0                         |

|                 | 4000 | 0x4001 3400 - 0x4001 37FF | Reserved                       |

|                 | APB2 | 0x4001 3000 - 0x4001 33FF | SPI0                           |

|                 |      | 0x4001 2C00 - 0x4001 2FFF | TIMER0                         |

|                 |      | 0x4001 2800 - 0x4001 2BFF | Reserved                       |

|                 |      | 0x4001 2400 - 0x4001 27FF | ADC                            |

|                 |      | 0x4001 0800 - 0x4001 23FF | Reserved                       |

|                 |      | 0x4001 0400 - 0x4001 07FF | EXTI                           |

|                 |      | 0x4001 0000 - 0x4001 03FF | SYSCFG                         |

|                 | 455  | 0x4000 C400 - 0x4000 FFFF | Reserved                       |

|                 | APB1 | 0x4000 C000 - 0x4000 C3FF | Reserved                       |

# GD32F130xx Datasheet

|     |                                          | BUSZF ISUXX DalaSneel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bus | Address                                  | Peripherals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 0x4000 7C00 - 0x4000 BFFF                | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     | 0x4000 7800 - 0x4000 7BFF                | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     | 0x4000 7400 - 0x4000 77FF                | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     | 0x4000 7000 - 0x4000 73FF                | PMU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     | 0x4000 6400 - 0x4000 6FFF                | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     | 0x4000 6000 - 0x4000 63FF                | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     | 0x4000 5C00 - 0x4000 5FFF                | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     | 0x4000 5800 - 0x4000 5BFF                | I2C1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     | 0x4000 5400 - 0x4000 57FF                | I2C0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     | 0x4000 4800 - 0x4000 53FF                | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     | 0x4000 4400 - 0x4000 47FF                | USART1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 0x4000 4000 - 0x4000 43FF                | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     | 0x4000 3C00 - 0x4000 3FFF                | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     | 0x4000 3800 - 0x4000 3BFF                | SPI1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     | 0x4000 3400 - 0x4000 37FF                | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     | 0x4000 3000 - 0x4000 33FF                | FWDGT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     | 0x4000 2C00 - 0x4000 2FFF                | WWDGT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5   | 0x4000 2800 - 0x4000 2BFF                | RTC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     | 0x4000 2400 - 0x4000 27FF                | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     | 0x4 <mark>0</mark> 00 2000 - 0x4000 23FF | TIMER13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | 0x4000 1400 - 0x4000 1FFF                | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     | 0x4000 1000 - 0x4000 13FF                | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     | 0x4000 0800 - 0x4000 0FFF                | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     | 0x4000 0400 - 0x4000 07FF                | TIMER2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 0x4000 0000 - 0x4000 03FF                | TIMER1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 0x2000 2000 - 0x3FFF FFFF                | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     | 0x2000 0000 - 0x2000 1FFF                | SRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     | 0x1FFF F810 - 0x1FFF FFFF                | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     | 0x1FFF F800 - 0x1FFF F80F                | Option bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     | 0x1FFF EC00 - 0x1FFF F7FF                | System memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | 0x0801 0000 - 0x1FFF EBFF                | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     | 0x0800 0000 - 0x0800 FFFF                | Main Flash memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | 0x0000 0000 - 0x07FF FFFF                | Aliased to Flash or system memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | Bus                                      | 0x4000 7C00 - 0x4000 BFFF  0x4000 7800 - 0x4000 7BFF  0x4000 7400 - 0x4000 77FF  0x4000 7000 - 0x4000 73FF  0x4000 6000 - 0x4000 6FFF  0x4000 5800 - 0x4000 5FFF  0x4000 5400 - 0x4000 5FFF  0x4000 5400 - 0x4000 57FF  0x4000 4400 - 0x4000 57FF  0x4000 4000 - 0x4000 37FF  0x4000 3C00 - 0x4000 3FFF  0x4000 3C00 - 0x4000 3FFF  0x4000 3800 - 0x4000 3FFF  0x4000 3000 - 0x4000 37FF  0x4000 3000 - 0x4000 37FF  0x4000 2C00 - 0x4000 2FFF  0x4000 2800 - 0x4000 2FFF  0x4000 2400 - 0x4000 27FF  0x4000 1000 - 0x4000 17FF  0x4000 1000 - 0x4000 17FF  0x4000 1000 - 0x4000 17FF  0x4000 1000 - 0x4000 07FF  0x4000 0800 - 0x4000 07FF  0x4000 0800 - 0x4000 07FF  0x4000 0000 - 0x4000 07FF  0x1FFF F810 - 0x1FFF FFFF  0x1FFF F800 - 0x1FFF F8FF  0x1FFF F800 - 0x1FFF F7FF  0x0801 0000 - 0x0800 FFFF |

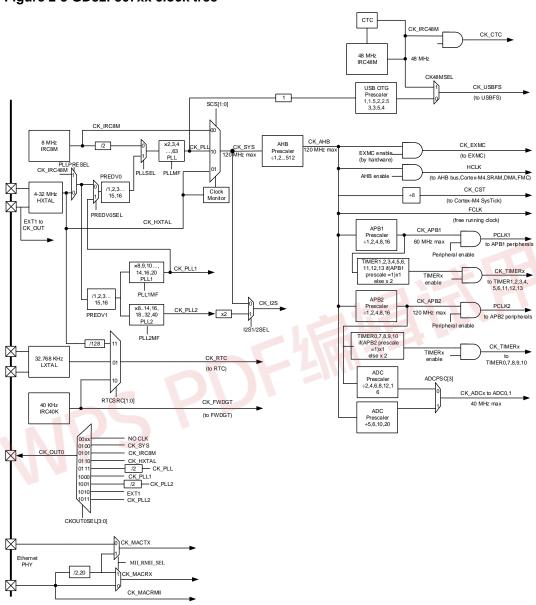

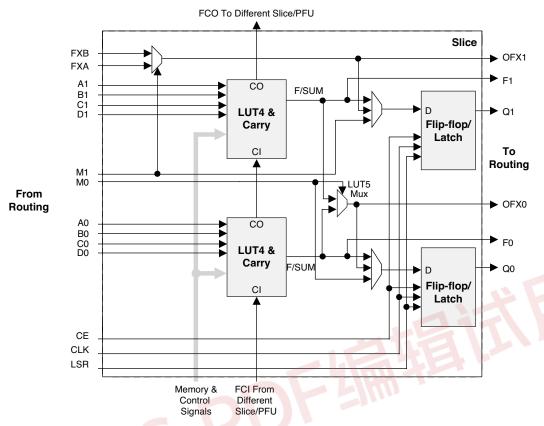

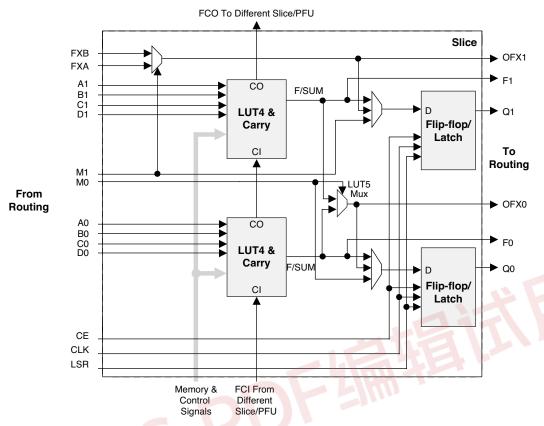

## 2.5. Clock tree

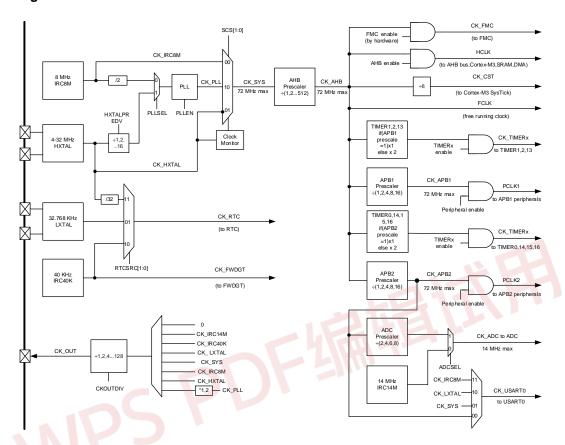

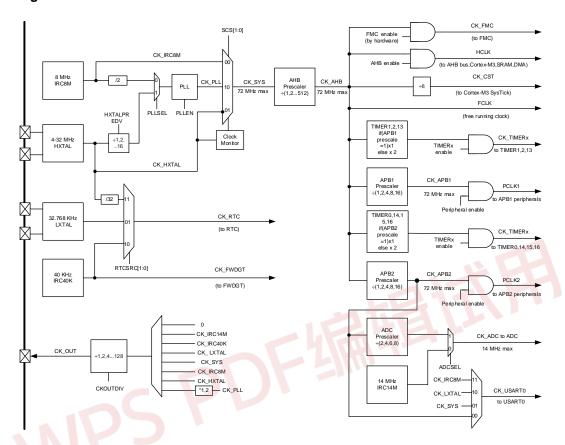

Figure 2-8. GD32F130xx clock tree

### Legend:

HXTAL: High speed crystal oscillator LXTAL: Low speed crystal oscillator IRC8M: Internal 8M RC oscillators IRC40K: Internal 40K RC oscillator IRC14M: Internal 14M RC oscillators

# 2.6. Pin definitions

# 2.6.1. GD32F130R8 LQFP64 pin definitions

Table 2-3. GD32F130R8 LQFP64 pin definitions

| Table 2-3. GD32F130R8   |      |                            | LWIIOT                      | pin deminions                                                                                              |

|-------------------------|------|----------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------|

| Pin Name                | Pins | Pin<br>Type <sup>(1)</sup> | I/O<br>Level <sup>(2)</sup> | Functions description                                                                                      |

| $V_{BAT}$               | 1    | Р                          |                             | Default: V <sub>BAT</sub>                                                                                  |

| PC13-<br>TAMPER-<br>RTC | 2    | I/O                        |                             | Default: PC13<br>Additional: RTC_TAMP0, RTC_TS, RTC_OUT, WKUP1                                             |

| PC14-<br>OSC32IN        | 3    | I/O                        |                             | Default: PC14 Additional: OSC32IN                                                                          |

| PC15-<br>OSC32OU<br>T   | 4    | I/O                        |                             | Default: PC15<br>Additional: OSC32OUT                                                                      |

| PF0-<br>OSCIN           | 5    | I/O                        | 5VT                         | Default: PF0 Additional: OSCIN                                                                             |

| PF1-<br>OSCOUT          | 6    | I/O                        | 5VT                         | Default: PF1 Additional: OSCOUT                                                                            |

| NRST                    | 7    | I/O                        |                             | Default: NRST                                                                                              |

| PC0                     | 8    | I/O                        |                             | Default: PC0 Alternate: EVENTOUT Additional: ADC_IN10                                                      |

| PC1                     | 9    | I/O                        |                             | Default: PC1 Alternate: EVENTOUT Additional: ADC_IN11                                                      |

| PC2                     | 10   | I/O                        |                             | Default: PC2 Alternate: EVENTOUT Additional: ADC_IN12                                                      |

| PC3                     | 11   | I/O                        |                             | Default: PC3 Alternate: EVENTOUT Additional: ADC_IN13                                                      |

| Vssa                    | 12   | Р                          |                             | Default: V <sub>SSA</sub>                                                                                  |

| $V_{DDA}$               | 13   | Р                          |                             | Default: V <sub>DDA</sub>                                                                                  |

| PA0-WKUP                | 14   | I/O                        |                             | Default: PA0 Alternate: USART1_CTS, TIMER1_CH0, TIMER1_ETI, I2C1_SCL Additional: ADC_IN0, RTC_TAMP1, WKUP0 |

| PA1                     | 15   | I/O                        |                             | Default: PA1 Alternate: USART1_RTS, TIMER1_CH1, I2C1_SDA,                                                  |

|          |      |                            |                             | GD32F130XX DataStieet                                                                                                |

|----------|------|----------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------|

| Pin Name | Pins | Pin<br>Type <sup>(1)</sup> | I/O<br>Level <sup>(2)</sup> | Functions description                                                                                                |

|          |      |                            |                             | EVENTOUT Additional: ADC IN1                                                                                         |

| PA2      | 16   | I/O                        |                             | Default: PA2 Alternate: USART1_TX, TIMER1_CH2, TIMER14_CH0 , Additional: ADC_IN2                                     |

| PA3      | 17   | I/O                        |                             | Default: PA3 Alternate: USART1_RX, TIMER1_CH3, TIMER14_CH1 Additional: ADC_IN3                                       |

| PF4      | 18   | I/O                        | 5VT                         | Default: PF4 Alternate: SPI1_NSS, EVENTOUT                                                                           |

| PF5      | 19   | I/O                        | 5VT                         | Default: PF5 Alternate: EVENTOUT                                                                                     |

| PA4      | 20   | I/O                        |                             | Default: PA4 Alternate: SPI0_NSS, USART1_CK, TIMER13_CH0, SPI1_NSS                                                   |

| PA5      | 21   | I/O                        |                             | Additional: ADC_IN4  Default: PA5  Alternate: SPI0_SCK, TIMER1_CH0, TIMER1_ETI  Additional: ADC_IN5                  |

| PA6      | 22   | I/O                        |                             | Default: PA6 Alternate: SPI0_MISO, TIMER2_CH0, TIMER0_BRKIN, TIMER15_CH0, EVENTOUT Additional: ADC_IN6               |

| PA7      | 23   | I/O                        |                             | Default: PA7 Alternate: SPI0_MOSI, TIMER2_CH1, TIMER13_CH0, TIMER0_CH0_ON, TIMER16_CH0, EVENTOUT Additional: ADC_IN7 |

| PC4      | 24   | I/O                        |                             | Default: PC4 Alternate: EVENTOUT Additional: ADC_IN14                                                                |

| PC5      | 25   | I/O                        |                             | Default: PC5 Additional: ADC_IN15                                                                                    |

| PB0      | 26   | I/O                        |                             | Default: PB0 Alternate: TIMER2_CH2, TIMER0_CH1_ON, USART1_RX, EVENTOUT Additional: ADC_IN8                           |

| PB1      | 27   | I/O                        |                             | Default: PB1 Alternate: TIMER2_CH3, TIMER13_CH0, TIMER0_CH2_ON, SPI1_SCK Additional: ADC_IN9                         |

| PB2      | 28   | I/O                        | 5VT                         | Default: PB2                                                                                                         |

| PB10     | 29   | I/O                        | 5VT                         | Default: PB10 Alternate: I2C1_SCL, TIMER1_CH2                                                                        |

| Pin Name | Pins | Pin<br>Type <sup>(1)</sup> | I/O<br>Level <sup>(2)</sup> | Functions description                                                                                |

|----------|------|----------------------------|-----------------------------|------------------------------------------------------------------------------------------------------|

| PB11     | 30   | I/O                        | 5VT                         | Default: PB11 Alternate: I2C1_SDA, TIMER1_CH3, EVENTOUT                                              |

| Vss      | 31   | Р                          |                             | Default: V <sub>SS</sub>                                                                             |

| $V_{DD}$ | 32   | Р                          |                             | Default: V <sub>DD</sub>                                                                             |

| PB12     | 33   | I/O                        |                             | Default: PB12<br>Alternate: SPI1_NSS, TIMER0_BRKIN, I2C1_SMBA,<br>EVENTOUT                           |

| PB13     | 34   | I/O                        | 5VT                         | Default: PB13<br>Alternate: SPI1_SCK, TIMER0_CH0_ON                                                  |

| PB14     | 35   | I/O                        | 5VT                         | Default: PB14 Alternate: SPI1_MISO, TIMER0_CH1_ON, TIMER14_CH0                                       |

| PB15     | 36   | I/O                        | 5VT                         | Default: PB15 Alternate: SPI1_MOSI, TIMER0_CH2_ON, TIMER14_CH0_ON, TIMER14_CH1 Additional: RTC_REFIN |

| PC6      | 37   | I/O                        | 5VT                         | Default: PC6 Alternate: TIMER2_CH0                                                                   |

| PC7      | 38   | I/O                        | 5VT                         | Default: PC7 Alternate: TIMER2_CH1                                                                   |

| PC8      | 39   | I/O                        | 5VT                         | De <mark>fault:</mark> PC8<br>Alternate: TIMER2_CH2                                                  |

| PC9      | 40   | I/O                        | 5VT                         | Default: PC9 Alternate: TIMER2_CH3                                                                   |

| PA8      | 41   | I/O                        | 5VT                         | Default: PA8 Alternate: USART0_CK, TIMER0_CH0, CK_OUT, USART1_TX, EVENTOUT                           |

| PA9      | 42   | I/O                        | 5VT                         | Default: PA9 Alternate: USART0_TX, TIMER0_CH1, TIMER14_BRKIN, I2C0_SCL                               |

| PA10     | 43   | I/O                        |                             | Default: PA10<br>Alternate: USART0_RX, TIMER0_CH2, TIMER16_BRKIN,<br>I2C0_SDA                        |

| PA11     | 44   | I/O                        | 5VT                         | Default: PA11 Alternate: USART0_CTS, TIMER0_CH3, EVENTOUT                                            |

| PA12     | 45   | I/O                        | 5VT                         | Default: PA12<br>Alternate: USART0_RTS, TIMER0_ETI, EVENTOUT                                         |

| PA13     | 46   | I/O                        | 5VT                         | Default: PA13<br>Alternate: IFRP_OUT, SWDIO, SPI1_MISO                                               |

| PF6      | 47   | I/O                        | 5VT                         | Default: PF6 Alternate: I2C1_SCL                                                                     |

| PF7      | 48   | I/O                        | 5VT                         | Default: PF7<br>Alternate: I2C1_SDA                                                                  |

| Pin Name | Pins | Pin<br>Type <sup>(1)</sup> | I/O<br>Level <sup>(2)</sup> | Functions description                                                                    |

|----------|------|----------------------------|-----------------------------|------------------------------------------------------------------------------------------|

| PA14     | 49   | I/O                        | 5VT                         | Default: PA14 Alternate: USART1_TX, SWCLK, SPI1_MOSI                                     |

| PA15     | 50   | I/O                        | 5VT                         | Default: PA15 Alternate: SPI0_NSS, USART1_RX, TIMER1_CH0, TIMER1_ETI, SPI1_NSS, EVENTOUT |

| PC10     | 51   | I/O                        | 5VT                         | Default: PC10                                                                            |

| PC11     | 52   | I/O                        | 5VT                         | Default: PC11                                                                            |

| PC12     | 53   | I/O                        | 5VT                         | Default: PC12                                                                            |

| PD2      | 54   | I/O                        | 5VT                         | Default: PD2 Alternate: TIMER2_ETI                                                       |

| PB3      | 55   | I/O                        | 5VT                         | Default: PB3 Alternate: SPI0_SCK, TIMER1_CH1, EVENTOUT                                   |

| PB4      | 56   | I/O                        | 5VT                         | Default: PB4 Alternate: SPI0_MISO, TIMER2_CH0, EVENTOUT                                  |

| PB5      | 57   | I/O                        | 5VT                         | Default: PB5 Alternate: SPI0_MOSI, I2C0_SMBA, TIMER15_BRKIN, TIMER2_CH1                  |

| PB6      | 58   | I/O                        | 5VT                         | Default: PB6 Alternate: I2C0_SCL, USART0_TX, TIMER15_CH0_ON                              |

| PB7      | 59   | I/O                        | 5VT                         | Default: PB7 Alternate: I2C0_SDA, USART0_RX, TIMER16_CH0_ON                              |

| воото    | 60   |                            |                             | Default: BOOT0                                                                           |

| PB8      | 61   | I/O                        | 5VT                         | Default: PB8 Alternate: I2C0_SCL, TIMER15_CH0                                            |

| PB9      | 62   | I/O                        | 5VT                         | Default: PB9 Alternate: I2C0_SDA, IFRP_OUT, TIMER16_CH0, EVENTOUT                        |

| Vss      | 63   | Р                          |                             | Default: Vss                                                                             |

| $V_{DD}$ | 64   | Р                          |                             | Default: V <sub>DD</sub>                                                                 |

- (1) Type: I = input, O = output, P = power.

- (2) I/O Level: 5VT = 5 V tolerant.

# 2.6.2. GD32F130Cx LQFP48 pin definitions

Table 2-4. GD32F130Cx LQFP48 pin definitions

| Table 2-4. G            | JJZF I | JUCK L                     | ≪1⁻Γ40                      | oin definitions                                                                                                                                                       |

|-------------------------|--------|----------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                | Pins   | Pin<br>Type <sup>(1)</sup> | I/O<br>Level <sup>(2)</sup> | Functions description                                                                                                                                                 |

| $V_{BAT}$               | 1      | Р                          |                             | Default: V <sub>BAT</sub>                                                                                                                                             |

| PC13-<br>TAMPER-<br>RTC | 2      | I/O                        |                             | Default: PC13<br>Additional: RTC_TAMP0, RTC_TS, RTC_OUT, WKUP1                                                                                                        |

| PC14-<br>OSC32IN        | 3      | I/O                        |                             | Default: PC14<br>Additional: OSC32IN                                                                                                                                  |

| PC15-<br>OSC32OUT       | 4      | I/O                        |                             | Default: PC15<br>Additional: OSC32OUT                                                                                                                                 |

| PF0-OSCIN               | 5      | I/O                        | 5VT                         | Default: PF0<br>Additional: OSCIN                                                                                                                                     |

| PF1-<br>OSCOUT          | 6      | I/O                        | 5VT                         | Default: PF1 Additional: OSCOUT                                                                                                                                       |

| NRST                    | 7      | I/O                        |                             | Default: NRST                                                                                                                                                         |

| Vssa                    | 8      | Р                          |                             | Default: VssA                                                                                                                                                         |

| $V_{DDA}$               | 9      | Р                          |                             | Default: V <sub>DDA</sub>                                                                                                                                             |

| PA0-WKUP                | 10     | I/O                        |                             | Default: PA0 Alternate: USART0_CTS <sup>(3)</sup> , USART1_CTS <sup>(4)</sup> , TIMER1_CH0, TIMER1_ETI, I2C1_SCL <sup>(5)</sup> Additional: ADC_IN0, RTC_TAMP1, WKUP0 |

| PA1                     | 11     | I/O                        |                             | Default: PA1 Alternate: USART0_RTS <sup>(3)</sup> , USART1_RTS <sup>(4)</sup> , TIMER1_CH1, I2C1_SDA <sup>(5)</sup> , EVENTOUT Additional: ADC_IN1                    |

| PA2                     | 12     | I/O                        |                             | Default: PA2 Alternate: USART0_TX <sup>(3)</sup> , USART1_TX <sup>(4)</sup> , TIMER1_CH2, TIMER14_CH0 Additional: ADC_IN2                                             |

| PA3                     | 13     | I/O                        |                             | Default: PA3 Alternate: USART0_RX <sup>(3)</sup> , USART1_RX <sup>(4)</sup> , TIMER1_CH3, TIMER14_CH1 Additional: ADC_IN3                                             |

| PA4                     | 14     | I/O                        |                             | Default: PA4 Alternate: SPI0_NSS, USART0_CK <sup>(3)</sup> , USART1_CK <sup>(4)</sup> , TIMER13_CH0, SPI1_NSS <sup>(5)</sup> Additional: ADC_IN4                      |

| PA5                     | 15     | I/O                        |                             | Default: PA5 Alternate: SPI0_SCK, TIMER1_CH0, TIMER1_ETI Additional: ADC_IN5                                                                                          |

| Pin Name | Pins   | Pin<br>Type <sup>(1)</sup> | I/O<br>Level <sup>(2)</sup> | Functions description                                                                                                                           |

|----------|--------|----------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| PA6      | 16     | I/O                        |                             | Default: PA6 Alternate: SPI0_MISO, TIMER2_CH0, TIMER0_BRKIN, TIMER15_CH0, EVENTOUT Additional: ADC_IN6                                          |

| PA7      | 17     | I/O                        |                             | Default: PA7 Alternate: SPI0_MOSI, TIMER2_CH1, TIMER13_CH0, TIMER0_CH0_ON, TIMER16_CH0, EVENTOUT Additional: ADC_IN7                            |

| PB0      | 18     | I/O                        |                             | Default: PB0 Alternate: TIMER2_CH2, TIMER0_CH1_ON, USART1_RX <sup>(4)</sup> , EVENTOUT Additional: ADC_IN8                                      |

| PB1      | 19 I/O | I/O                        |                             | Default: PB1 Alternate: TIMER2_CH3, TIMER13_CH0, TIMER0_CH2_ON, SPI1_SCK <sup>(5)</sup> Additional: ADC_IN9                                     |

| PB2      | 20     | I/O                        | 5VT                         | Default: PB2                                                                                                                                    |

| PB10     | 21     | I/O                        | 5VT                         | Default: PB10 Alternate: I2C1_SCL <sup>(5)</sup> , TIMER1_CH2                                                                                   |

| PB11     | 22     | I/O                        | 5VT                         | Default: PB11 Alternate: I2C1_SDA <sup>(5)</sup> , TIMER1_CH3, EVENTOUT                                                                         |